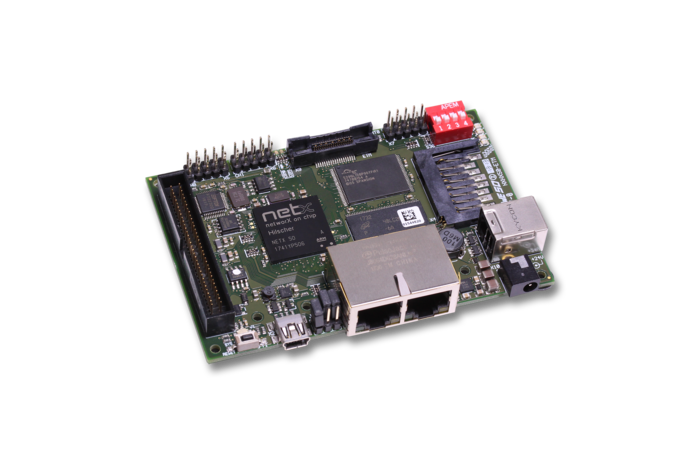

netX è un controller di rete altamente integrato con una nuova architettura di sistema ottimizzata per la comunicazione e il massimo throughput dei dati.

Tramite una memoria integrata a due porte, funge da chip complementare su una CPU host. Dai sistemi di bus di campo ai sistemi Real-Time Ethernet, netX copre l’intera gamma di comunicazioni industriali. Se l’applicazione non giustifica un’ulteriore CPU, l’interfaccia host può essere configurata come bus di estensione o direttamente come ingresso e uscita digitale.

La CPU ARM 966E-S a 32 bit, con clock a 200 MHz, ha una RAM interna da 112 KB e una memoria ROM da 64 KB. Tramite il controller di memoria a 32 bit, la memoria può essere estesa esternamente e in modo flessibile con SDRAM, SRAM o FLASH.

Funzioni periferiche estese, interfacce seriali come UART, USB, SPI, I²C, nonché il controller IO-Link e CCD integrato consentono un’ampia varietà di applicazioni.

Lo switch dati centrale e i canali di comunicazione liberamente configurabili con la loro intelligenza rappresentano la caratteristica unica e distintiva di netX come controller di rete high-end. Tramite cinque percorsi dati, lo switch dati collega la CPU ARM e i controller di comunicazione, host e DMA alla memoria o alle unità periferiche. I controller trasmettono quindi i dati in parallelo, contrariamente alla tradizionale architettura sequenziale, con un solo bus dati comune e cicli di allocazione bus aggiuntivi.

I controller dei due canali di comunicazione sono identici e hanno una struttura a due livelli. Sono costituiti da ALU dedicate e unità logiche speciali che ricevono la loro funzione di protocollo tramite microcodice. I PHY sono integrati per Ethernet, dunque il circuito esterno per Ethernet è ridotto a componenti passivi come trasformatori e componenti RC.

Il Medium Access Controller xMAC invia o riceve i dati in base al rispettivo processo di accesso al bus e codifica o converte i dati in una rappresentazione a byte.

Il Protocol Execution Controller xPEC compila i dati in pacchetti e controlla il traffico dei telegrammi. Grandi quantità di dati vengono scambiate blocco a blocco tramite DMA con la memoria ARM, mentre ogni canale dispone di una memoria a due porte per le informazioni sullo stato. In alternativa, viene implementata una logica di buffer triplo che fornisce sempre l’indirizzo del buffer libero successivo per consentire uno scambio di dati privo di conflitti.

Con le ALU di comunicazione intelligente, netX realizza i protocolli e le combinazioni di protocolli più diversificati in un unico chip, una nuovissima funzione nella tecnologia di comunicazione industriale.