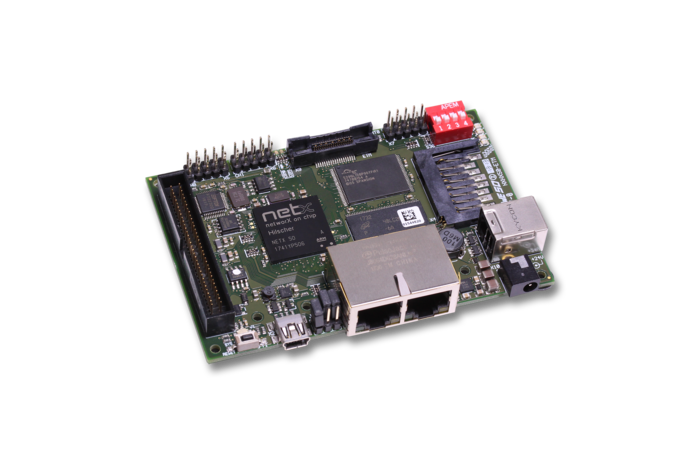

The netX is a highly integrated network controller with a new system architecture optimized for communication and maximum data throughput.

Via an integrated dual-port memory it acts as a companion chip on a host CPU. From fieldbus systems to Real-Time Ethernet systems, the netX covers the whole range of industrial communication. If the application does not justify a further CPU, the host interface can be configured as an extension bus or directly as a digital input and output.

The 32-bit CPU ARM 966E-S, clocked with 200 MHz, has a 112 KByte internal RAM and a 64 KByte ROM memory. Via the 32-bit memory controller, the memory can be extended externally and flexibly with SDRAM, SRAM, or FLASH.

Extensive periphery functions, serial interfaces such as UART, USB, SPI, I²C, as well as the integrated IO-Link and CCD-controller enable a large variety of applications.

The central data switch and the freely configurable communication channels with their own intelligence represent the unique feature and distinguishing characteristic of the netX as a high-end network controller. Via five data paths the data switch connects the ARM CPU as well as the communication, host, and DMA controllers to the memory or the peripheral units. The controllers thus transmit the data in parallel, contrary to the traditional sequential architecture with merely one common data bus and additional bus allocation cycles.

The controllers of the two communication channels are identical and have a two-level structure. They consist of dedicated ALUs and special logic units that receive their protocol function via microcode. The PHYs are integrated for Ethernet, i. e. the external circuit for Ethernet is reduced to passive components such as transformers and RC components.

The Medium Access Controller xMAC sends or receives the data according to the respective bus access process and encodes or converts the data into a byte representation.

The Protocol Execution Controller xPEC compiles the data into packets and controls the telegram traffic. Large data amounts are exchanged block-by-block via DMA with the ARM memory while each channel has a dual-port memory for status information. As an alternative, a triple buffer logic is implemented which always provides the address of the next free buffer to enable a conflict-free data exchange.

With the intelligent communication ALUs, the netX realizes the most diverse protocols and protocol combinations in one chip – a brand new feature in the industrial communication technology.