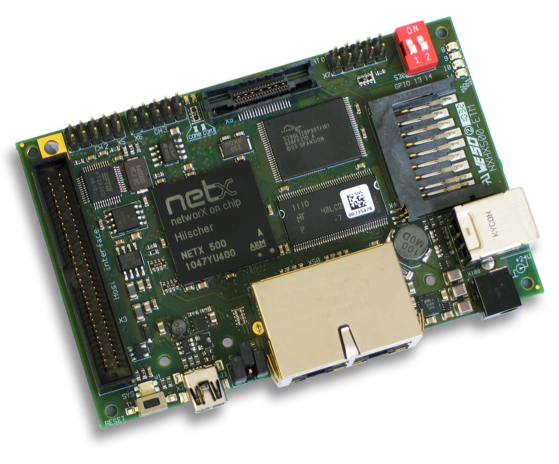

Basé sur le processeur 32 bits ARM 926EJ-S cadencé à 200 MHz, le netX est doté d'une unité de gestion de mémoire, de caches, d’un DSP et d'extensions Java. La mémoire RAM interne de 144 Ko et la mémoire ROM de 32 Ko, qui contient le chargeur de démarrage, suffisent pour les applications de plus petite taille. Pour Windows CE et Linux, la mémoire est étendue en externe par SDRAM, SRAM ou FLASH. La connexion à un hôte supérieur s'effectue via l'interface de la mémoire à double accès, qui peut également être configurée comme bus d'extension 16 bits pour les applications autonomes.

Des fonctions périphériques complètes, des interfaces série telles que UART, USB, SPI et I²C permettent une grande variété d'applications. Le commutateur central de données et trois canaux de communication librement configurables avec leur propre intelligence représentent la caractéristique unique et distinctive du netX en tant que contrôleur réseau « haut de gamme ». Le commutateur de données relie le processeur ARM ainsi que les contrôleurs de communication et hôte à la mémoire ou aux unités périphériques via cinq chemins de données. Les contrôleurs transmettent donc les données en parallèle, contrairement à l'architecture séquentielle traditionnelle avec un seul bus de données commun et des cycles d'allocation de bus supplémentaires.

Les contrôleurs des trois canaux de communication sont identiques et ont une structure à deux niveaux. Ils se composent d'unités UAL dédiées et d'unités logiques spéciales qui reçoivent leur fonction de protocole par microcode. Deux canaux contiennent en outre une puce PHY pour Ethernet intégré.

Le contrôleur d'accès au support xMAC envoie ou reçoit les données selon le processus d'accès au bus correspondant et code ou convertit les données en octets.

Le gestionnaire de protocole (Protocol Execution Controller) xPEC compile les données en paquets et contrôle le trafic de télégrammes.

Les données sont échangées bloc par bloc via transfert DMA avec la mémoire ARM. Comme alternative, chaque canal dispose d'une mémoire à double accès pour les informations d'état ou comme mémoire de données process locale.