Ethernet xpic mac peripheral module driver.

- Revision

- 4646

- Date

- 2018-12-19 08:47:36 +0100 (Mi, 19 Dez 2018)

- Copyright

- Copyright (c) Hilscher Gesellschaft fuer Systemautomation mbH. All Rights Reserved.

- Note

- Exclusion of Liability for this demo software: The following software is intended for and must only be used for reference and in an evaluation laboratory environment. It is provided without charge and is subject to alterations. There is no warranty for the software, to the extent permitted by applicable law. Except when otherwise stated in writing the copyright holders and/or other parties provide the software "as is" without warranty of any kind, either expressed or implied. Please refer to the Agreement in README_DISCLAIMER.txt, provided together with this file! By installing or otherwise using the software, you accept the terms of this Agreement. If you do not agree to the terms of this Agreement, then do not install or use the Software!

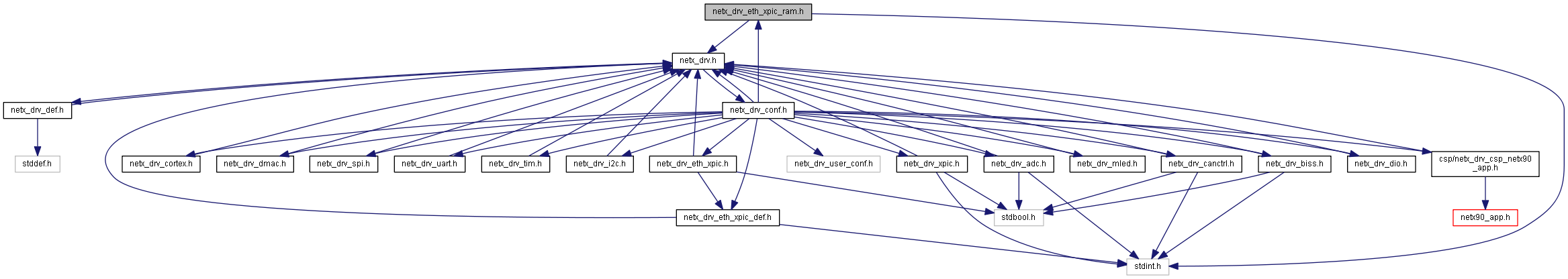

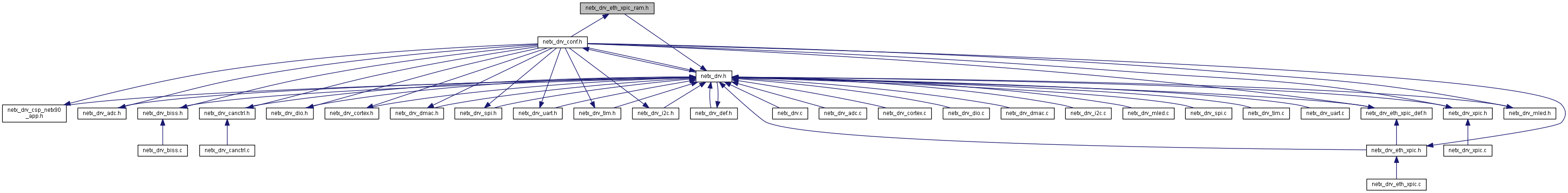

Definition in file netx_drv_eth_xpic_ram.h.