|

| #define | DRV_ADC_CONFIG_DEFAULT |

| | Default parameter for the initialization of DRV_ADC_CONFIGURATION_T. More...

|

| |

| #define | DRV_ADC_SEQ_MEAS_CONFIG_DEFAULT |

| | Default parameter for the initialization of DRV_ADC_MEAS_CONFIGURATION_T. More...

|

| |

| #define | DRV_ADC_SEQ_CONFIG_DEFAULT |

| | Default parameter for the initialization of DRV_ADC_SEQ_CONFIGURATION_T. More...

|

| |

| #define | DRV_ADC_SEQ_CATCHED_NO_RESULT 0xffff |

| | Result was not accessible after the measurement. More...

|

| |

| #define | DRV_ADC_INITIALIZER (DRV_ADC_HANDLE_T){0, {0, 0, 0, 0}, DRV_ADC_CONFIG_DEFAULT, DRV_LOCK_INITIALIZER_VALUE} |

| | Default settings for adc device driver. More...

|

| |

| #define | DRV_ADC_SEQ_INITIALIZER (DRV_ADC_SEQ_HANDLE_T){0, 0, DRV_ADC_SEQ_CONFIG_DEFAULT, DRV_LOCK_INITIALIZER_VALUE, {0, 0, 0, 0, 0, 0}} |

| | Default settings for adc sequencer. More...

|

| |

|

| enum | DRV_ADC_SEQ_DEVICE_MSK_E {

DRV_ADC_SEQ_DEVICE_MSK_0 = 0x1u,

DRV_ADC_SEQ_DEVICE_MSK_1 = 0x2u,

DRV_ADC_SEQ_DEVICE_MSK_2 = 0x4u,

DRV_ADC_SEQ_DEVICE_MSK_3 = 0x8u,

DRV_ADC_SEQ_DEVICE_MSK_MIN = DRV_ADC_SEQ_DEVICE_MSK_0,

DRV_ADC_SEQ_DEVICE_MSK_MAX = 0xFu

} |

| | The adc sequencer device IDs. More...

|

| |

| enum | DRV_ADC_VREF_BUFFER_E {

DRV_ADC_VREF_BUFFER_ENABLED = 0x1u,

DRV_ADC_VREF_BUFFER_DISABLED = 0x0u,

DRV_ADC_VREF_BUFFER_MIN = DRV_ADC_VREF_BUFFER_DISABLED,

DRV_ADC_VREF_BUFFER_MAX = DRV_ADC_VREF_BUFFER_ENABLED

} |

| | Use internal 2.6V reference: More...

|

| |

| enum | DRV_ADC_SEQ_DMA_MODE_E {

DRV_ADC_SEQ_DMA_MODE_ENABLED = 0x0u,

DRV_ADC_SEQ_DMA_MODE_DISABLED = 0x1u,

DRV_ADC_SEQ_DMA_MODE_MIN = DRV_ADC_SEQ_DMA_MODE_ENABLED,

DRV_ADC_SEQ_DMA_MODE_MAX = DRV_ADC_SEQ_DMA_MODE_DISABLED

} |

| | Enable or Disable the DMA mode. More...

|

| |

| enum | DRV_ADC_SEQ_32Bit_MODE_E {

DRV_ADC_SEQ_32Bit_MODE_ENABLED = 0x1u,

DRV_ADC_SEQ_32Bit_MODE_DISABLED = 0x0u,

DRV_ADC_SEQ_32Bit_MODE_MIN = DRV_ADC_SEQ_32Bit_MODE_DISABLED,

DRV_ADC_SEQ_32Bit_MODE_MAX = DRV_ADC_SEQ_32Bit_MODE_ENABLED

} |

| | The copy engine only uses 32bit addresses and DWord access. This mode wastes memory but speeds up the copy by not running read-modify-write cycles. If deactivated, the default 16bit addresses and Word access is used. More...

|

| |

| enum | DRV_ADC_SEQ_VREF_VDD3_E {

DRV_ADC_SEQ_VREF_VDD3_ENABLED = 0x1u,

DRV_ADC_SEQ_VREF_VDD3_DISABLED = 0x0u,

DRV_ADC_SEQ_VREF_VDD3_MIN = DRV_ADC_SEQ_VREF_VDD3_DISABLED,

DRV_ADC_SEQ_VREF_VDD3_MAX = DRV_ADC_SEQ_VREF_VDD3_ENABLED

} |

| | Use core voltage of 3.3V as reference or use Vref of the adc (which can be external or 2.6V). More...

|

| |

| enum | DRV_ADC_SEQ_CLK_SYNC_E {

DRV_ADC_SEQ_CLK_SYNC_DISABLED = 0x0u,

DRV_ADC_SEQ_CLK_SYNC_ENABLED = 0x1u,

DRV_ADC_SEQ_CLK_SYNC_MIN = DRV_ADC_SEQ_CLK_SYNC_DISABLED,

DRV_ADC_SEQ_CLK_SYNC_MAX = DRV_ADC_SEQ_CLK_SYNC_ENABLED

} |

| | Synchronization of the adc clocks. More...

|

| |

| enum | DRV_ADC_SEQ_CLK_PHASE_E {

DRV_ADC_SEQ_CLK_PHASE_DEFAULT = 0xFFu,

DRV_ADC_SEQ_CLK_PHASE_MIN = 0x00u,

DRV_ADC_SEQ_CLK_PHASE_MAX = 0xFFu

} |

| | Generation of the rising edge of the adcclk is delayed until the global clk_phase counter matches this value. NOTE: The rising edge of the adcclk ending the first sample period of a triggered measurement is NEVER delayed. More...

|

| |

| enum | DRV_ADC_SEQ_CLK_PERIOD_E {

DRV_ADC_SEQ_CLK_PERIOD_DEFAULT = 0x2u,

DRV_ADC_SEQ_CLK_PERIOD_MIN = 0x00u,

DRV_ADC_SEQ_CLK_PERIOD_MAX = 0xFFu

} |

| | Duration of an adcclk period in system clock cycles-1. More...

|

| |

| enum | DRV_ADC_SEQ_CHANNEL_TRACKING_TIME_E {

DRV_ADC_SEQ_CHANNEL_TRACKING_TIME_DEFAULT = 0x4u,

DRV_ADC_SEQ_CHANNEL_TRACKING_TIME_MIN = 0x00u,

DRV_ADC_SEQ_CHANNEL_TRACKING_TIME_MAX = 0xFFu

} |

| | ADC sample extension for input channel 0. More...

|

| |

| enum | DRV_ADC_SEQ_MEASUREMENT_E {

DRV_ADC_SEQ_MEASUREMENT_0 = 0u,

DRV_ADC_SEQ_MEASUREMENT_1 = 1u,

DRV_ADC_SEQ_MEASUREMENT_2 = 2u,

DRV_ADC_SEQ_MEASUREMENT_3 = 3u,

DRV_ADC_SEQ_MEASUREMENT_4 = 4u,

DRV_ADC_SEQ_MEASUREMENT_5 = 5u,

DRV_ADC_SEQ_MEASUREMENT_6 = 6u,

DRV_ADC_SEQ_MEASUREMENT_7 = 7u,

DRV_ADC_SEQ_MEASUREMENT_MIN = DRV_ADC_SEQ_MEASUREMENT_0,

DRV_ADC_SEQ_MEASUREMENT_MAX = DRV_ADC_SEQ_MEASUREMENT_7

} |

| | Measurements of the sequencer. More...

|

| |

| enum | DRV_ADC_SEQ_MEAS_ENABLE_E {

DRV_ADC_SEQ_MEAS_DISABLE = 0x0u,

DRV_ADC_SEQ_MEAS_ENABLE = 0x1u,

DRV_ADC_SEQ_MEAS_ENABLE_MIN = DRV_ADC_SEQ_MEAS_DISABLE,

DRV_ADC_SEQ_MEAS_ENABLE_MAX = DRV_ADC_SEQ_MEAS_ENABLE

} |

| | Enable measurement configuration. More...

|

| |

| enum | DRV_ADC_SEQ_MEAS_ADR_OFFSET_E {

DRV_ADC_SEQ_BASE_ADR_OFFSET_NONE = 0x00u,

DRV_ADC_SEQ_BASE_ADR_OFFSET_MIN = DRV_ADC_SEQ_BASE_ADR_OFFSET_NONE,

DRV_ADC_SEQ_BASE_ADR_OFFSET_MAX = 0x1Fu

} |

| | Address offset specified in 16 bit words where the sum will be stored. More...

|

| |

| enum | DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_E {

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_0 = 0x0u,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_1 = 0x1u,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_2 = 0x2u,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_3 = 0x3u,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_4 = 0x4u,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_5 = 0x5u,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_6 = 0x6u,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_7 = 0x7u,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_MIN = DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_0,

DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_MAX = DRV_ADC_SEQ_MEAS_INPUT_CHANNEL_7

} |

| | Input channel multiplexer setting. More...

|

| |

| enum | DRV_ADC_SEQ_MEAS_OVERSAMPLING_E {

DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_1 = 0x0ul,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_2 = 0x1ul,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_3 = 0x2ul,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_4 = 0x3ul,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_5 = 0x4ul,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_6 = 0x5ul,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_7 = 0x6ul,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_8 = 0x7ul,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_MIN = DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_1,

DRV_ADC_SEQ_MEAS_OVERSAMPLING_MAX = DRV_ADC_SEQ_MEAS_OVERSAMPLING_SUM_8

} |

| | Number of samples minus one to sum for this measurement i.e. 0:sum 1 samples, 1:sum 2 samples, ... More...

|

| |

| enum | DRV_ADC_SEQ_MEAS_TRIGGER_E {

DRV_ADC_SEQ_MEAS_TRIGGER_CONDITION_MIN = 0x0ul,

DRV_ADC_SEQ_MEAS_TRIGGER_CONDITION_MAX = 0x0FFFFul,

DRV_ADC_SEQ_MEAS_TRIGGER_DELAYED_DTEVT_0 = 0x10000ul,

DRV_ADC_SEQ_MEAS_TRIGGER_DELAYED_DTEVT_1 = 0x10001ul,

DRV_ADC_SEQ_MEAS_TRIGGER_DELAYED_DTEVT_2 = 0x10002ul,

DRV_ADC_SEQ_MEAS_TRIGGER_DELAYED_DTEVT_3 = 0x10003ul,

DRV_ADC_SEQ_MEAS_TRIGGER_DELAYED_DTEVT_4 = 0x10004ul,

DRV_ADC_SEQ_MEAS_TRIGGER_DELAYED_DTEVT_5 = 0x10005ul,

DRV_ADC_SEQ_MEAS_TRIGGER_GPIO_APP_COUNTER_0 = 0x10006ul,

DRV_ADC_SEQ_MEAS_TRIGGER_GPIO_APP_COUNTER_1 = 0x10007ul,

DRV_ADC_SEQ_MEAS_TRIGGER_GPIO_APP_COUNTER_2 = 0x10008ul,

DRV_ADC_SEQ_MEAS_TRIGGER_POS_EDGE_XC_TRIGGER_0 = 0x10009ul,

DRV_ADC_SEQ_MEAS_TRIGGER_NEG_EDGE_XC_TRIGGER_0 = 0x1000aul,

DRV_ADC_SEQ_MEAS_TRIGGER_POS_EDGE_XC_TRIGGER_1 = 0x1000bul,

DRV_ADC_SEQ_MEAS_TRIGGER_NEG_EDGE_XC_TRIGGER_1 = 0x1000cul,

DRV_ADC_SEQ_MEAS_TRIGGER_POS_EDGE_XC_SAMPLE_0 = 0x1000dul,

DRV_ADC_SEQ_MEAS_TRIGGER_NEG_EDGE_XC_SAMPLE_0 = 0x1000eul,

DRV_ADC_SEQ_MEAS_TRIGGER_POS_EDGE_XC_SAMPLE_1 = 0x1000ful,

DRV_ADC_SEQ_MEAS_TRIGGER_NEG_EDGE_XC_SAMPLE_1 = 0x10010ul,

DRV_ADC_SEQ_MEAS_TRIGGER_RESERVED_MIN = 0x10011ul,

DRV_ADC_SEQ_MEAS_TRIGGER_RESERVED_MAX = 0x1FFFEul,

DRV_ADC_SEQ_MEAS_TRIGGER_IMMEDIATELY = 0x1FFFFul,

DRV_ADC_SEQ_MEAS_TRIGGER_MIN = DRV_ADC_SEQ_MEAS_TRIGGER_CONDITION_MIN,

DRV_ADC_SEQ_MEAS_TRIGGER_MAX = DRV_ADC_SEQ_MEAS_TRIGGER_IMMEDIATELY

} |

| | Trigger condition for measurement. More...

|

| |

| enum | DRV_ADC_SEQ_CONTINUOUS_MODE_E {

DRV_ADC_SEQ_CONTINUOUS_MODE_DISABLED = 0x0ul,

DRV_ADC_SEQ_CONTINUOUS_MODE_ENABLED = 0x1ul,

DRV_ADC_SEQ_CONTINUOUS_MODE_MIN = DRV_ADC_SEQ_CONTINUOUS_MODE_DISABLED,

DRV_ADC_SEQ_CONTINUOUS_MODE_MAX = DRV_ADC_SEQ_CONTINUOUS_MODE_ENABLED

} |

| | Continuous or Single Shot mode of the device and api. More...

|

| |

| enum | DRV_ADC_SEQ_BASE_ADDRESS_E {

DRV_ADC_SEQ_BASE_ADDRESS_MIN = 0x00000000u,

DRV_ADC_SEQ_BASE_ADDRESS_MAX = 0xFFFFFFFFu

} |

| | Base address for writing the measurement results. More...

|

| |

| enum | DRV_ADC_CLK_PERIOD_E {

DRV_ADC_CLK_PERIOD_DEFAULT = 2u,

DRV_ADC_CLK_PERIOD_MIN = 0u,

DRV_ADC_CLK_PERIOD_MAX = 0xffu

} |

| | Max value of global ADC synchronization counter: More...

|

| |

| enum | DRV_ADC_STATE_MEASUREMENT_E {

DRV_ADC_STATE_MEASUREMENT_0 = 0u,

DRV_ADC_STATE_MEASUREMENT_1 = 1u,

DRV_ADC_STATE_MEASUREMENT_2 = 2u,

DRV_ADC_STATE_MEASUREMENT_3 = 3u,

DRV_ADC_STATE_MEASUREMENT_4 = 4u,

DRV_ADC_STATE_MEASUREMENT_5 = 5u,

DRV_ADC_STATE_MEASUREMENT_6 = 6u,

DRV_ADC_STATE_MEASUREMENT_7 = 7u,

DRV_ADC_STATE_MEASUREMENT_IDLE = 8u,

DRV_ADC_STATE_MEASUREMENT_MAX = DRV_ADC_STATE_MEASUREMENT_IDLE

} |

| | The enumeration for the available measurements. More...

|

| |

| enum | DRV_ADC_SOFT_RESET_E {

DRV_ADC_SOFT_RESET_ACTIVE = 0u,

DRV_ADC_SOFT_RESET_INACTIVE = 1u,

DRV_ADC_SOFT_RESET_MIN = DRV_ADC_SOFT_RESET_ACTIVE,

DRV_ADC_SOFT_RESET_MAX = DRV_ADC_SOFT_RESET_INACTIVE

} |

| | Soft-Reset configuration of the ADCs. More...

|

| |

| enum | DRV_ADC_POWER_DOWN_E {

DRV_ADC_DISABLE = 0u,

DRV_ADC_ENABLE = 1u,

DRV_ADC_POWER_DOWN_MIN = DRV_ADC_DISABLE,

DRV_ADC_POWER_DOWN_MAX = DRV_ADC_ENABLE

} |

| | Power-down mode configuration of the ADCs. More...

|

| |

| enum | DRV_ADC_DEADTIME_E {

DRV_ADC_DEADTIME_DEFAULT = 0x000au,

DRV_ADC_DEADTIME_MIN = 0x0000u,

DRV_ADC_DEADTIME_MAX = 0xffffu

} |

| | Dead time delay configuration of the ADCs. More...

|

| |

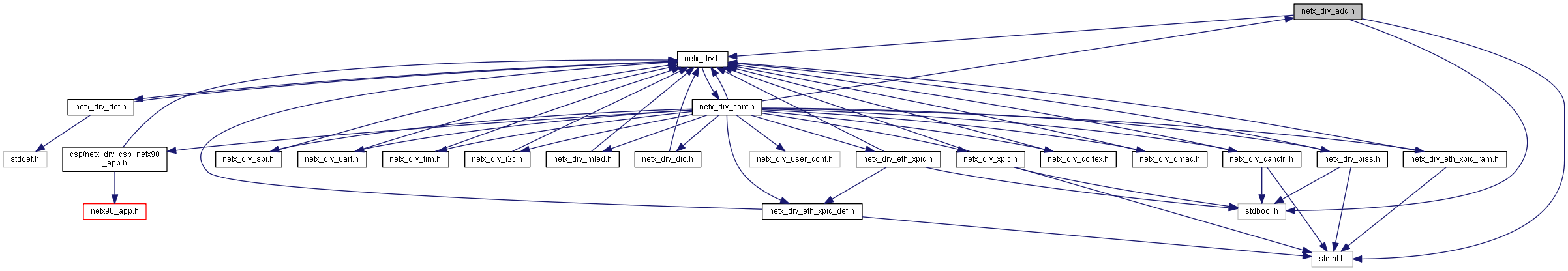

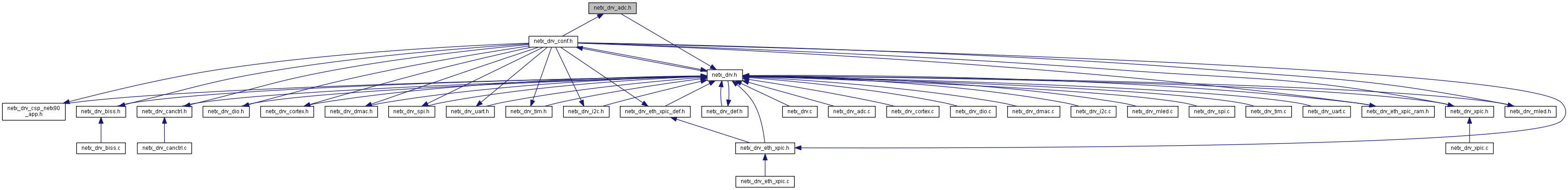

Header file of ADC DRV module.

- Revision

- 6124

- Date

- 2019-08-28 19:41:54 +0200 (Mi, 28 Aug 2019)

- Copyright

- Copyright (c) Hilscher Gesellschaft fuer Systemautomation mbH. All Rights Reserved.

- Note

- Exclusion of Liability for this demo software: The following software is intended for and must only be used for reference and in an evaluation laboratory environment. It is provided without charge and is subject to alterations. There is no warranty for the software, to the extent permitted by applicable law. Except when otherwise stated in writing the copyright holders and/or other parties provide the software "as is" without warranty of any kind, either expressed or implied. Please refer to the Agreement in README_DISCLAIMER.txt, provided together with this file! By installing or otherwise using the software, you accept the terms of this Agreement. If you do not agree to the terms of this Agreement, then do not install or use the Software!

Definition in file netx_drv_adc.h.