|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

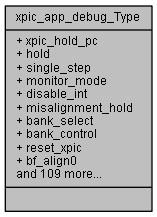

xpic_app_debug (xpic_app_debug) More...

#include <netx90_app.h>

xpic_app_debug (xpic_app_debug)

Definition at line 30475 of file netx90_app.h.

| union { ... } |

< (@ 0xFF884080) xpic_app_debug Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t xpic_app_debug_Type::bank_control |

[6..6] control over the register bank selection WARNING: reset this BIT to 0 BEFORE start xPIC (clear hold bits)

Definition at line 30496 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::bank_select |

[5..5] Select register bank (0: default bank, 1: fiq bank) Access registers in xpic_regs area (xpic_r0 .. xpic_r7, xpic_stat)

Definition at line 30494 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::bf_align0 |

[31..8] bitField alignment value for aeabi compatibility

[31..9] bitField alignment value for aeabi compatibility

[31..5] bitField alignment value for aeabi compatibility

[31..1] bitField alignment value for aeabi compatibility

Definition at line 30502 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::bf_align0 |

[31..10] bitField alignment value for aeabi compatibility

[31..5] bitField alignment value for aeabi compatibility

[31..1] bitField alignment value for aeabi compatibility

[31..4] bitField alignment value for aeabi compatibility

Definition at line 30646 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::break0 |

[2..2] Breakpoint 0 is active(read only)

Definition at line 30638 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::break0_irq |

[0..0] Breakpoint 0 Interrupt

Definition at line 30659 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::break0_irq |

[0..0] Breakpoint 0 Interrupt

Definition at line 30674 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::break0_read_data |

[7..7] Breakpoint 0 last load access (read only)

Definition at line 30643 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::break1 |

[3..3] Breakpoint 1 is active(read only)

Definition at line 30639 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::break1_irq |

[1..1] Breakpoint 1 Interrupt

Definition at line 30660 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::break1_irq |

[1..1] Breakpoint 1 Interrupt

Definition at line 30675 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::break1_read_data |

[8..8] Breakpoint 1 last load access (read only)

Definition at line 30644 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::chain |

[6..6] Breakpoint 0 input from Breakpoint 1

[6..6] reserved value

Definition at line 30548 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::data_access |

[3..3] Breakpoint 0 (1: data access, 0: instruction fetch)

[3..3] Breakpoint 1 (1: data access, 0: instruction fetch)

Definition at line 30545 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::data_misalignment |

[6..6] Data Misaligment is active(read only)

Definition at line 30642 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::disable_int |

[3..3] disable interrupts

Definition at line 30489 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::enable |

| __IM uint32_t xpic_app_debug_Type::fiq_enable |

[3..3] FIQ enable bit

Definition at line 30802 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::fiq_mode |

[4..4] Breakpoint 0 xPIC in FIQ Mode

[4..4] Breakpoint 1 xPIC in FIQ Mode

Definition at line 30546 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::fiq_status |

[1..1] FIQ status

Definition at line 30800 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::hold |

[0..0] 0: Start xPIC 1: Hold xPIC

Definition at line 30481 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::hold |

[1..1] global HOLD BIT status 0- start xPIC, 1- hold xPIC (read only)

Definition at line 30636 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::irq_enable |

[2..2] IRQ enable bit

Definition at line 30801 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::irq_mode |

[5..5] Breakpoint 0 xPIC in IRQ Mode

[5..5] Breakpoint 1 xPIC in IRQ Mode

Definition at line 30547 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::irq_status |

[0..0] IRQ status

Definition at line 30799 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::mas |

[2..1] Breakpoint 0 memory access size (00: byte. 01: word, 10 dword, 11 reserved)

[2..1] Breakpoint 1 memory access size (00: byte. 01: word, 10 dword, 11 reserved)

Definition at line 30543 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::misalignment_hold |

[4..4] 0: xPIC triggers misalignment_irq on misaligned memory accesses but does not stop. 1: xPIC stops after a misaligned memory accesses and triggers misalignment_irq. Write '1' into xpic_break_irq_raw.misalignment_irq to continue.

Definition at line 30490 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::misalignment_irq |

[4..4] Data Misalignment Error Interrupt

[0..0] Data Misalignment Error Interrupt

Definition at line 30663 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::misalignment_irq |

[4..4] Data Misalignment Error Interrupt

[0..0] Data Misalignment Error Interrupt

Definition at line 30678 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::monitor_mode |

[2..2] 0: xPIC stops when hardware breakpoint is triggered. Write '1' into xpic_break_irq_raw.break0_irq or break1_irq to continue. 1: Hardware breakpoints still generate irqs but do not stop the xPIC.

Definition at line 30485 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::range |

[7..7] Breakpoint 0 input from Breakpoint 1

[7..7] reserved value

Definition at line 30549 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::reset_xpic |

[7..7] REQUEST reset all internal internal states and the pipeline EXCEPT: the internal register (r0-r7, usr0-4), bank0 and bank1 reset this registers manually EXCEPT: xpic hard_breaker/debug registers 1 - xPIC reset request

Definition at line 30498 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::single_step |

[1..1] 0: Disable single step mode 1: xPIC processes a single pipeline step then stops and triggers the single_step_irq. Write '1' into xpic_break_irq_raw.single_step_irq to continue.

Definition at line 30482 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::single_step |

[5..5] Single Step Break is active(read only)

Definition at line 30641 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::single_step_irq |

[3..3] single step Breakpoint Interrupt

Definition at line 30662 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::single_step_irq |

[3..3] single step Breakpoint Interrupt

Definition at line 30677 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::soft_break |

[4..4] Software Break is active(read only)

Definition at line 30640 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::soft_break_irq |

[2..2] Software Breakpoint Interrupt

Definition at line 30661 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::soft_break_irq |

[2..2] Software Breakpoint Interrupt

Definition at line 30676 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::val |

[31..0] Breakpoint 0 address value

[31..0] Breakpoint 0 address mask

[31..0] Breakpoint 0 data value (for data access only)

[31..0] Breakpoint 0 data mask (for data access only)

[7..0] Breakpoint 0 control mask

[31..0] Breakpoint 1 address value

[31..0] Breakpoint 1 address mask

[31..0] Breakpoint 1 data value (for data access only)

[31..0] Breakpoint 1 data mask (for data access only)

[7..0] Breakpoint 1 control mask

Definition at line 30510 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::val |

[31..0] last PC

[31..0] xPIC FIQ return value

[31..0] xPIC last IRQ return value

Definition at line 30626 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::write |

[0..0] Breakpoint 0 write/read access

[0..0] Breakpoint 1 write/read access

Definition at line 30542 of file netx90_app.h.

| __IOM uint32_t xpic_app_debug_Type::xpic_break0_addr |

(@ 0x00000004) no Register description

Definition at line 30507 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break0_addr_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break0_addr_mask |

(@ 0x00000008) no Register description

Definition at line 30515 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break0_addr_mask_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break0_contr |

(@ 0x00000014) no Register description

Definition at line 30539 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break0_contr_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break0_contr_mask |

(@ 0x00000018) no Register description

Definition at line 30556 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break0_contr_mask_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break0_data |

(@ 0x0000000C) no Register description

Definition at line 30523 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break0_data_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break0_data_mask |

(@ 0x00000010) no Register description

Definition at line 30531 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break0_data_mask_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break1_addr |

(@ 0x0000001C) no Register description

Definition at line 30565 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break1_addr_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break1_addr_mask |

(@ 0x00000020) no Register description

Definition at line 30573 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break1_addr_mask_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break1_contr |

(@ 0x0000002C) no Register description

Definition at line 30597 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break1_contr_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break1_contr_mask |

(@ 0x00000030) no Register description

Definition at line 30614 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break1_contr_mask_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break1_data |

(@ 0x00000024) no Register description

Definition at line 30581 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break1_data_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break1_data_mask |

(@ 0x00000028) no Register description

Definition at line 30589 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break1_data_mask_b |

| __IM uint32_t xpic_app_debug_Type::xpic_break_irq_masked |

(@ 0x00000040) xPIC_DEBUG Masked IRQ register for other CPU (ARM): Shows status of masked IRQs (as connected to ARM)

Definition at line 30669 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_irq_masked_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break_irq_msk_reset |

(@ 0x00000048) xPIC_DEBUG interrupt mask reset for other CPU (ARM): This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit (disables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 30708 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_irq_msk_reset_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break_irq_msk_set |

(@ 0x00000044) xPIC_DEBUG interrupt mask set for other CPU (ARM): The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit (enables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating

Definition at line 30684 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_irq_msk_set_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break_irq_raw |

(@ 0x0000003C) xPIC_DEBUG Raw IRQ register: Read access shows status of unmasked IRQs. IRQs are set automatically and reset by writing to this register: Write access with '1' resets the appropriate IRQ. Write access with '0' does not influence this bit.

Definition at line 30651 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_irq_raw_b |

| __IM uint32_t xpic_app_debug_Type::xpic_break_last_pc |

(@ 0x00000034) no Register description

Definition at line 30623 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_last_pc_b |

| __IM uint32_t xpic_app_debug_Type::xpic_break_own_irq_masked |

(@ 0x0000004C) xPIC_DEBUG own Masked IRQ register (for xPIC): Shows status of masked IRQs (as connected to xPIC)

Definition at line 30729 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_own_irq_masked_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break_own_irq_msk_reset |

(@ 0x00000054) xPIC_DEBUG own interrupt mask reset (for XPIC): This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit (disables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 30760 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_own_irq_msk_reset_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_break_own_irq_msk_set |

(@ 0x00000050) xPIC_DEBUG own interrupt mask set (for xPIC): The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit (enables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating inte

Definition at line 30740 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_own_irq_msk_set_b |

| __IM uint32_t xpic_app_debug_Type::xpic_break_return_fiq_pc |

(@ 0x00000058) xPIC_DEBUG information FIQ return PC value valid if xPIC is in FIQ

Definition at line 30777 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_return_fiq_pc_b |

| __IM uint32_t xpic_app_debug_Type::xpic_break_return_irq_pc |

(@ 0x0000005C) xPIC_DEBUG information last IRQ return PC value valid if xPIC is in IRQ

Definition at line 30786 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_return_irq_pc_b |

| __IM uint32_t xpic_app_debug_Type::xpic_break_status |

(@ 0x00000038) Read access shows the reason why xPIC is in HOLD / BREAK

Definition at line 30631 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_break_status_b |

| __IOM uint32_t xpic_app_debug_Type::xpic_hold_pc |

(@ 0x00000000) no Register description

Definition at line 30478 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_hold_pc_b |

| __IM uint32_t xpic_app_debug_Type::xpic_in_hold |

[0..0] xPIC is in Break or Hold (read only)

Definition at line 30635 of file netx90_app.h.

| __IM uint32_t xpic_app_debug_Type::xpic_irq_status |

(@ 0x00000060) Read access shows the xpic irq status and the xpic irq enable bits

Definition at line 30795 of file netx90_app.h.

| struct { ... } xpic_app_debug_Type::xpic_irq_status_b |

| __IM uint32_t xpic_app_debug_Type::xpic_reset_status |

[9..9] 1 = XPIC ist in Reset(read only)

Definition at line 30645 of file netx90_app.h.