|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

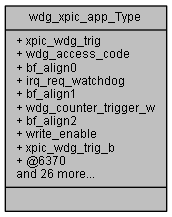

wdg_xpic_app (wdg_xpic_app) More...

#include <netx90_app.h>

wdg_xpic_app (wdg_xpic_app)

Definition at line 31358 of file netx90_app.h.

| union { ... } |

< (@ 0xFF900180) wdg_xpic_app Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t wdg_xpic_app_Type::bf_align0 |

[23..20] bitField alignment value for aeabi compatibility

[31..16] bitField alignment value for aeabi compatibility

[31..1] bitField alignment value for aeabi compatibility

Definition at line 31369 of file netx90_app.h.

| __IM uint32_t wdg_xpic_app_Type::bf_align0 |

[31..17] bitField alignment value for aeabi compatibility

[31..1] bitField alignment value for aeabi compatibility

Definition at line 31392 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::bf_align1 |

[27..25] bitField alignment value for aeabi compatibility

Definition at line 31372 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::bf_align2 |

[30..29] bitField alignment value for aeabi compatibility

Definition at line 31375 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::irq_req_watchdog |

[24..24] xPIC IRQ request of watchdog, writing 1 deletes IRQ to xPIC

Definition at line 31370 of file netx90_app.h.

| __IM uint32_t wdg_xpic_app_Type::val |

[16..0] Actual watchdog counter value: Bit 16 shows: 1: Watchdog is counting down from xpic_irq_timeout to 0 for xPIC-IRQ 0: Watchdog is counting down from arm_irq_timeout to 0 for ARM-IRQ

Definition at line 31388 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::val |

[15..0] Watchdog interrupt timeout The total xpic_irq timeout for a netX clock of 100MHz is: xpic_wdg_xpic_irq_timeout 100us

[15..0] Watchdog ARM interrupt timeout The total arm_irq timeout for a netX clock of 100MHz is: (xpic_wdg_xpic_irq_timeout

Definition at line 31402 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::wdg_access_code |

[19..0] Watchdog access code for triggering. A read access gives the next 16 bit code for trigger. A write access with correct access code will trigger the watchdog counter.

Definition at line 31366 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::wdg_arm_irq |

[0..0] Interrupt from xPIC Watchdog to ARM

Definition at line 31430 of file netx90_app.h.

| __IM uint32_t wdg_xpic_app_Type::wdg_arm_irq |

[0..0] Interrupt from xPIC Watchdog to ARM

Definition at line 31440 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::wdg_counter_trigger_w |

[28..28] Watchdog trigger bit: Bit must be set to trigger the watchdog counter. When read, this bit is always '0'

Definition at line 31373 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::write_enable |

[31..31] Write enable bit for timeout register: As long as this bit is not set all write accesses to the timeout register are ignored.

Definition at line 31376 of file netx90_app.h.

| __IOM uint32_t wdg_xpic_app_Type::xpic_wdg_arm_irq_timeout |

(@ 0x0000000C) netX xPIC Watchdog ARM interrupt timout register: xpic_irq_timeout or arm_irq_timeout must be nonzero to enable watchdog

Definition at line 31410 of file netx90_app.h.

| struct { ... } wdg_xpic_app_Type::xpic_wdg_arm_irq_timeout_b |

| __IM uint32_t wdg_xpic_app_Type::xpic_wdg_counter |

(@ 0x00000004) netX xPIC Watchdog Counter Register The counter value is decremented each 10000 system clock cycles.

Definition at line 31383 of file netx90_app.h.

| struct { ... } wdg_xpic_app_Type::xpic_wdg_counter_b |

| __IM uint32_t wdg_xpic_app_Type::xpic_wdg_irq_masked |

(@ 0x00000014) xpic_wdg Masked IRQ register: Shows status of masked IRQs (as connected to xPIC).

Definition at line 31436 of file netx90_app.h.

| struct { ... } wdg_xpic_app_Type::xpic_wdg_irq_masked_b |

| __IOM uint32_t wdg_xpic_app_Type::xpic_wdg_irq_msk_reset |

(@ 0x0000001C) xpic_wdg interrupt mask disable: This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit (disables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 31466 of file netx90_app.h.

| struct { ... } wdg_xpic_app_Type::xpic_wdg_irq_msk_reset_b |

| __IOM uint32_t wdg_xpic_app_Type::xpic_wdg_irq_msk_set |

(@ 0x00000018) xpic_wdg interrupt mask enable: The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit (enables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating interrupt mask, de

Definition at line 31446 of file netx90_app.h.

| struct { ... } wdg_xpic_app_Type::xpic_wdg_irq_msk_set_b |

| __IOM uint32_t wdg_xpic_app_Type::xpic_wdg_irq_raw |

(@ 0x00000010) Read access shows status of unmasked IRQs. IRQs are set automatically and reset by writing to this register: Write access with '1' resets the appropriate IRQ. Write access with '0' does not influence this bit.

Definition at line 31423 of file netx90_app.h.

| struct { ... } wdg_xpic_app_Type::xpic_wdg_irq_raw_b |

| __IOM uint32_t wdg_xpic_app_Type::xpic_wdg_trig |

(@ 0x00000000) netX xPIC Watchdog Trigger Register. The watchdog access code is generated by a pseudo random generator.

Definition at line 31361 of file netx90_app.h.

| struct { ... } wdg_xpic_app_Type::xpic_wdg_trig_b |

| __IOM uint32_t wdg_xpic_app_Type::xpic_wdg_xpic_irq_timeout |

(@ 0x00000008) netX xPIC Watchdog xPIC interrupt timout register: xpic_irq_timeout or arm_irq_timeout must be nonzero to enable watchdog

Definition at line 31397 of file netx90_app.h.

| struct { ... } wdg_xpic_app_Type::xpic_wdg_xpic_irq_timeout_b |