|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

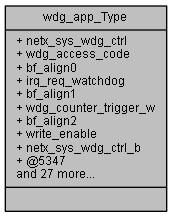

wdg_app (wdg_app) More...

#include <netx90_app.h>

wdg_app (wdg_app)

Definition at line 25551 of file netx90_app.h.

| union { ... } |

< (@ 0xFF801700) wdg_app Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t wdg_app_Type::bf_align0 |

[23..20] bitField alignment value for aeabi compatibility

[31..16] bitField alignment value for aeabi compatibility

[31..1] bitField alignment value for aeabi compatibility

Definition at line 25567 of file netx90_app.h.

| __IM uint32_t wdg_app_Type::bf_align0 |

[31..17] bitField alignment value for aeabi compatibility

[31..1] bitField alignment value for aeabi compatibility

Definition at line 25585 of file netx90_app.h.

| __IOM uint32_t wdg_app_Type::bf_align1 |

[27..25] bitField alignment value for aeabi compatibility

Definition at line 25569 of file netx90_app.h.

| __IOM uint32_t wdg_app_Type::bf_align2 |

[30..29] bitField alignment value for aeabi compatibility

Definition at line 25572 of file netx90_app.h.

| __IOM uint32_t wdg_app_Type::irq_req_watchdog |

[24..24] IRQ request of watchdog, writing 1 deletes IRQ

Definition at line 25568 of file netx90_app.h.

| __IM uint32_t wdg_app_Type::netx_sys_wdg |

(@ 0x00000004) netX System Watchdog Register The counter value is decremented each 10000 system clock cycles.

Definition at line 25580 of file netx90_app.h.

| struct { ... } wdg_app_Type::netx_sys_wdg_b |

| __IOM uint32_t wdg_app_Type::netx_sys_wdg_ctrl |

(@ 0x00000000) netX System Watchdog Trigger Register. The watchdog access code is generated by a pseudo random generator. It must be written correctly for a valid write access to this register (not only for triggering e.g. also for IRQ clearing). Note: WDGACT signal is available as MMIO function..

Definition at line 25554 of file netx90_app.h.

| struct { ... } wdg_app_Type::netx_sys_wdg_ctrl_b |

| __IM uint32_t wdg_app_Type::netx_sys_wdg_irq_masked |

(@ 0x00000014) netX System Wachtdog Masked IRQ register: Read access shows status of masked IRQs.

Definition at line 25627 of file netx90_app.h.

| struct { ... } wdg_app_Type::netx_sys_wdg_irq_masked_b |

| __IOM uint32_t wdg_app_Type::netx_sys_wdg_irq_msk_reset |

(@ 0x0000001C) netX System Wachtdog interrupt mask disable: This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit (disables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 25657 of file netx90_app.h.

| struct { ... } wdg_app_Type::netx_sys_wdg_irq_msk_reset_b |

| __IOM uint32_t wdg_app_Type::netx_sys_wdg_irq_msk_set |

(@ 0x00000018) netX System Wachtdog interrupt mask enable: The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit (enables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating interr

Definition at line 25637 of file netx90_app.h.

| struct { ... } wdg_app_Type::netx_sys_wdg_irq_msk_set_b |

| __IOM uint32_t wdg_app_Type::netx_sys_wdg_irq_raw |

(@ 0x00000010) netX System Wachtdog IRQ raw register: Read access shows status of unmasked IRQs. IRQs are set automatically and reset by writing to this register: Write access with '1' resets the appropriate IRQ. Write access with '0' does not influence this bit.

Definition at line 25613 of file netx90_app.h.

| struct { ... } wdg_app_Type::netx_sys_wdg_irq_raw_b |

| __IOM uint32_t wdg_app_Type::netx_sys_wdg_irq_timeout |

(@ 0x00000008) netX System Wachtdog Interrupt Timout Register

Definition at line 25590 of file netx90_app.h.

| struct { ... } wdg_app_Type::netx_sys_wdg_irq_timeout_b |

| __IOM uint32_t wdg_app_Type::netx_sys_wdg_res_timeout |

(@ 0x0000000C) netX System Watchdog Reset Timeout Register

Definition at line 25601 of file netx90_app.h.

| struct { ... } wdg_app_Type::netx_sys_wdg_res_timeout_b |

| __IOM uint32_t wdg_app_Type::wdg_access_code |

[19..0] Watchdog trigger and control register access code. A read access gives the next 16 bit code for writing the 'netx_sys_wdg_ctrl' register. A write access with correct access code will trigger the watchdog counter.

Definition at line 25563 of file netx90_app.h.

| __IM uint32_t wdg_app_Type::wdg_counter |

[16..0] Actual watchdog counter value

Definition at line 25584 of file netx90_app.h.

| __IOM uint32_t wdg_app_Type::wdg_counter_trigger_w |

[28..28] Watchdog trigger bit: Bit must be set to trigger the watchdog counter. When read, this bit is always '0'

Definition at line 25570 of file netx90_app.h.

| __IOM uint32_t wdg_app_Type::wdg_irq_timeout |

[15..0] Watchdog interrupt timeout The total netx_sys_irq timeout for a netX clock of 100MHz is: wdg_irq_timeout * 100us Note: The watchdog can be stopped by programming a 0.

Definition at line 25593 of file netx90_app.h.

| __IOM uint32_t wdg_app_Type::wdg_res_irq |

[0..0] Watchdog reset request timeout interrupt

Definition at line 25621 of file netx90_app.h.

| __IM uint32_t wdg_app_Type::wdg_res_irq |

[0..0] Watchdog reset request timeout interrupt

Definition at line 25631 of file netx90_app.h.

| __IOM uint32_t wdg_app_Type::wdg_res_timeout |

[15..0] Watchdog reset request timeout The total reset timeout for a netX clock of 100MHz is: (wdg_irq_timeout + wdg_res_timeout) 100us Note: The watchdog can be stopped by programming a 0.

Definition at line 25604 of file netx90_app.h.

| __IOM uint32_t wdg_app_Type::write_enable |

[31..31] Write enable bit for timeout register: As long as this bit is not set all write accesses to the timeout register are ignored.

Definition at line 25573 of file netx90_app.h.