|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

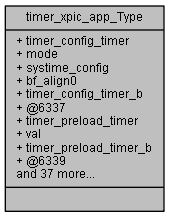

timer_xpic_app (timer_xpic_app) More...

#include <netx90_app.h>

timer_xpic_app (timer_xpic_app)

Definition at line 31188 of file netx90_app.h.

| union { ... } |

< (@ 0xFF900100) timer_xpic_app Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t timer_xpic_app_Type::bf_align0 |

[31..4] bitField alignment value for aeabi compatibility

[31..2] bitField alignment value for aeabi compatibility

Definition at line 31199 of file netx90_app.h.

| __IM uint32_t timer_xpic_app_Type::bf_align0 |

[31..4] bitField alignment value for aeabi compatibility

Definition at line 31290 of file netx90_app.h.

| __IOM uint32_t timer_xpic_app_Type::mode |

[1..0] Timer0 2'b00 : Timer stops at 0 2'b01 : Timer is preload with value from preload register at 0 2'b10 : Timer (value) compare with systime (once) 2'b11 : reserved

Definition at line 31194 of file netx90_app.h.

| __IOM uint32_t timer_xpic_app_Type::systime_config |

[3..2] systime for timer (2'b00.. systime_com, 2'b01.. systime_com_uc, 2'b10.. systime_app)

[1..0] systime for timer (2'b00.. systime_com, 2'b01.. systime_com_uc, 2'b10.. systime_app)

Definition at line 31197 of file netx90_app.h.

| __IOM uint32_t timer_xpic_app_Type::systime_s_irq |

[3..3] Systime sec Interrupt

Definition at line 31276 of file netx90_app.h.

| __IM uint32_t timer_xpic_app_Type::systime_s_irq |

[3..3] Systime sec Interrupt

Definition at line 31289 of file netx90_app.h.

| __IOM uint32_t timer_xpic_app_Type::timer0_irq |

[0..0] Timer 0 Interrupt

Definition at line 31273 of file netx90_app.h.

| __IM uint32_t timer_xpic_app_Type::timer0_irq |

[0..0] Timer 0 Interrupt

Definition at line 31286 of file netx90_app.h.

| __IOM uint32_t timer_xpic_app_Type::timer1_irq |

[1..1] Timer 1 Interrupt

Definition at line 31274 of file netx90_app.h.

| __IM uint32_t timer_xpic_app_Type::timer1_irq |

[1..1] Timer 1 Interrupt

Definition at line 31287 of file netx90_app.h.

| __IOM uint32_t timer_xpic_app_Type::timer2_irq |

[2..2] Timer 2 Interrupt

Definition at line 31275 of file netx90_app.h.

| __IM uint32_t timer_xpic_app_Type::timer2_irq |

[2..2] Timer 2 Interrupt

Definition at line 31288 of file netx90_app.h.

| __IOM uint32_t timer_xpic_app_Type::timer_compare_systime_s_value |

(@ 0x0000002C) SYSTIME sec compare value

Definition at line 31256 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_compare_systime_s_value_b |

| __IOM uint32_t timer_xpic_app_Type::timer_config_timer[3] |

(@ 0x00000000) ARM TIMER Config register0

Definition at line 31191 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_config_timer_b[3] |

| __IM uint32_t timer_xpic_app_Type::timer_irq_masked |

(@ 0x00000034) ARM_TIMER Masked IRQ register: Shows status of masked IRQs (as connected to ARM/xPIC)

Definition at line 31282 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_irq_masked_b |

| __IOM uint32_t timer_xpic_app_Type::timer_irq_msk_reset |

(@ 0x0000003C) ARM_TIMER interrupt mask reset: This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit (disables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 31318 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_irq_msk_reset_b |

| __IOM uint32_t timer_xpic_app_Type::timer_irq_msk_set |

(@ 0x00000038) ARM_TIMER interrupt mask set: The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit (enables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating interrupt mask, dele

Definition at line 31295 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_irq_msk_set_b |

| __IOM uint32_t timer_xpic_app_Type::timer_irq_raw |

(@ 0x00000030) ARM_TIMER Raw IRQ register: Read access shows status of unmasked IRQs. IRQs are set automatically and reset by writing to this register: Write access with '1' resets the appropriate IRQ. Write access with '0' does not influence this bit.

Definition at line 31265 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_irq_raw_b |

| __IOM uint32_t timer_xpic_app_Type::timer_preload_timer[3] |

(@ 0x0000000C) ARM TIMER Timer 0

Definition at line 31204 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_preload_timer_b[3] |

| __IOM uint32_t timer_xpic_app_Type::timer_systime_config |

(@ 0x00000040) Select systime for arm_timer_systime_(ns)s functions

Definition at line 31337 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_systime_config_b |

| __IM uint32_t timer_xpic_app_Type::timer_systime_ns |

(@ 0x00000028) ARM_TIMER lower SYSTIME register To allow consistent values of systime_s and systime_ns, lower bits of systime is latched to systime_ns, when systime_s is read. If no systime_s is read before (e.g. at 2nd read access of systime_ns), the actual value of systime_ns is read. This register should be dedicated to accesses via ARM. xPIC software should access systime via xpic_timer_systime_ns. Host software should access systime via DPM at systime_ns.

Definition at line 31236 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_systime_ns_b |

| __IM uint32_t timer_xpic_app_Type::timer_systime_s |

(@ 0x00000024) ARM_TIMER upper SYSTIME register To allow consistent values of systime_s and systime_ns, lower bits of systime is latched to systime_ns, when systime_s is read. This register should be dedicated to accesses via ARM. xPIC software should access systime via xpic_timer_systime_s. Host software should access systime via DPM at systime_s.

Definition at line 31220 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_systime_s_b |

| __IOM uint32_t timer_xpic_app_Type::timer_timer[3] |

(@ 0x00000018) ARM TIMER Timer 0

Definition at line 31212 of file netx90_app.h.

| struct { ... } timer_xpic_app_Type::timer_timer_b[3] |

| __IOM uint32_t timer_xpic_app_Type::val |

[31..0] preload value

[31..0] actual value of timer / systime compare value

[31..0] Compare value with systime_s (seconds): Systime_s_compare_irq is set, if systime_s matches.

Definition at line 31207 of file netx90_app.h.

| __IM uint32_t timer_xpic_app_Type::val |

[31..0] Systime high: Sample systime_ns at read access to systime_s. Value is incremented, if systime_ns reaches systime_border.

[31..0] Systime low: Sample systime_ns at read access to systime_s. Without sample read systime_s, read the actual value of systime_ns.

Definition at line 31230 of file netx90_app.h.