|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

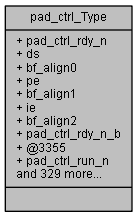

pad_ctrl (pad_ctrl) More...

#include <netx90_app.h>

Data Fields | |

| union { | |

| __IOM uint32_t pad_ctrl_rdy_n | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_rdy_n_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_run_n | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_run_n_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mled0 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 27 | |

| } pad_ctrl_mled0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mled1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 27 | |

| } pad_ctrl_mled1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mled2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 27 | |

| } pad_ctrl_mled2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mled3 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 27 | |

| } pad_ctrl_mled3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_com_io0 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_com_io0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_com_io1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_com_io1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_com_io2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_com_io2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_com_io3 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_com_io3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_uart_rxd | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_uart_rxd_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_uart_txd | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 27 | |

| } pad_ctrl_uart_txd_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_rxclk | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_rxclk_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_rxd0 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_rxd0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_rxd1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_rxd1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_rxd2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_rxd2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_rxd3 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_rxd3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_rxdv | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_rxdv_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_rxer | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_rxer_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_txclk | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_txclk_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_txd0 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_txd0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_txd1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_txd1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_txd2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_txd2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_txd3 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_txd3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_txen | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_txen_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_col | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_col_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_crs | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_crs_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_phy0_led_link_in | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_phy0_led_link_in_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_rxclk | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_rxclk_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_rxd0 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_rxd0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_rxd1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_rxd1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_rxd2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_rxd2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_rxd3 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_rxd3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_rxdv | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_rxdv_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_rxer | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_rxer_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_txclk | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_txclk_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_txd0 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_txd0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_txd1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_txd1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_txd2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_txd2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_txd3 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_txd3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_txen | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_txen_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_col | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_col_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_crs | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_crs_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_phy1_led_link_in | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_phy1_led_link_in_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii_mdc | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii_mdc_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii_mdio | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii_mdio_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_rst_out_n | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_rst_out_n_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_clk25out | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_clk25out_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_txen_bga2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_txen_bga2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_col_bga2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_col_bga2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii0_crs_bga2 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii0_crs_bga2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_phy0_led_link_in_bga2 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_phy0_led_link_in_bga2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_rxer_bga2 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_rxer_bga2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_col_bga2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_col_bga2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mii1_crs_bga2 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mii1_crs_bga2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_phy1_led_link_in_bga2 | |

| struct { | |

| __IOM uint32_t bf_align0: 4 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_phy1_led_link_in_bga2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mmio0 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mmio0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mmio1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mmio1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mmio2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mmio2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mmio3 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mmio3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mmio4 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mmio4_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mmio5 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mmio5_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mmio6 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mmio6_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_mmio7 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_mmio7_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_sqi_clk | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_sqi_clk_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_sqi_cs0n | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_sqi_cs0n_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_sqi_mosi | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_sqi_mosi_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_sqi_miso | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_sqi_miso_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_sqi_sio2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_sqi_sio2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_sqi_sio3 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_sqi_sio3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a0 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a3 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a4 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a4_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a5 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a5_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a6 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a6_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a7 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a7_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a8 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a8_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a9 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a9_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a10 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a10_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a11 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a11_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a12 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a12_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a13 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a13_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a14 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a14_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a15 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a15_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a16 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a16_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_a17 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_a17_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d0 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d0_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d1 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d1_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d2 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d2_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d3 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d3_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d4 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d4_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d5 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d5_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d6 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d6_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d7 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d7_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d8 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d8_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d9 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d9_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d10 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d10_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d11 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d11_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d12 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d12_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d13 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d13_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d14 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d14_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_d15 | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_d15_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_bhen | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_bhen_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_csn | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_csn_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_rdn | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_rdn_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_wrn | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_wrn_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_rdy | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_rdy_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_dirq | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_dirq_b | |

| }; | |

| union { | |

| __IOM uint32_t pad_ctrl_hif_sdclk | |

| struct { | |

| __IOM uint32_t ds: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t pe: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t ie: 1 | |

| __IOM uint32_t bf_align2: 25 | |

| } pad_ctrl_hif_sdclk_b | |

| }; | |

pad_ctrl (pad_ctrl)

Definition at line 10885 of file netx90_app.h.

| union { ... } |

< (@ 0xFF401000) pad_ctrl Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t pad_ctrl_Type::bf_align0 |

[3..1] bitField alignment value for aeabi compatibility

[3..0] bitField alignment value for aeabi compatibility

Definition at line 10902 of file netx90_app.h.

| __IOM uint32_t pad_ctrl_Type::bf_align1 |

[5..5] bitField alignment value for aeabi compatibility

[31..5] bitField alignment value for aeabi compatibility

Definition at line 10904 of file netx90_app.h.

| __IOM uint32_t pad_ctrl_Type::bf_align2 |

[31..7] bitField alignment value for aeabi compatibility

Definition at line 10906 of file netx90_app.h.

| __IOM uint32_t pad_ctrl_Type::ds |

[0..0] driving strength (low by default)

Definition at line 10901 of file netx90_app.h.

| __IOM uint32_t pad_ctrl_Type::ie |

[6..6] input enable (enabled by default)

[6..6] input enable (shared analog function, disabled by default)

[6..6] input enable (disabled by default)

Definition at line 10905 of file netx90_app.h.

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_clk25out |

(@ 0x000000BC) Pad configuration register of port CLK25OUT (asic_ctrl_access_k y protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11629 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_clk25out_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_com_io0 |

(@ 0x00000018) Pad configuration register of port COM_IO0 (asic_ctrl_access_ke protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc3) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 10983 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_com_io0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_com_io1 |

(@ 0x0000001C) Pad configuration register of port COM_IO1 (asic_ctrl_access_ke protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc3) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 10999 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_com_io1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_com_io2 |

(@ 0x00000020) Pad configuration register of port COM_IO2 (asic_ctrl_access_ke protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc3) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11015 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_com_io2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_com_io3 |

(@ 0x00000024) Pad configuration register of port COM_IO3 (asic_ctrl_access_ke protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc3) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11031 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_com_io3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a0 |

(@ 0x00000118) Pad configuration register of port HIF_A0 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11992 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a1 |

(@ 0x0000011C) Pad configuration register of port HIF_A1 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12008 of file netx90_app.h.

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a10 |

(@ 0x00000140) Pad configuration register of port HIF_A10 (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12152 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a10_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a11 |

(@ 0x00000144) Pad configuration register of port HIF_A11 (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12168 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a11_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a12 |

(@ 0x00000148) Pad configuration register of port HIF_A12 (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12184 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a12_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a13 |

(@ 0x0000014C) Pad configuration register of port HIF_A13 (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12200 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a13_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a14 |

(@ 0x00000150) Pad configuration register of port HIF_A14 (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12216 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a14_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a15 |

(@ 0x00000154) Pad configuration register of port HIF_A15 (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12232 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a15_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a16 |

(@ 0x00000158) Pad configuration register of port HIF_A16 (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12248 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a16_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a17 |

(@ 0x0000015C) Pad configuration register of port HIF_A17 (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12264 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a17_b |

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a2 |

(@ 0x00000120) Pad configuration register of port HIF_A2 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12024 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a3 |

(@ 0x00000124) Pad configuration register of port HIF_A3 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12040 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a4 |

(@ 0x00000128) Pad configuration register of port HIF_A4 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12056 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a4_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a5 |

(@ 0x0000012C) Pad configuration register of port HIF_A5 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12072 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a5_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a6 |

(@ 0x00000130) Pad configuration register of port HIF_A6 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12088 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a6_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a7 |

(@ 0x00000134) Pad configuration register of port HIF_A7 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12104 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a7_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a8 |

(@ 0x00000138) Pad configuration register of port HIF_A8 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12120 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a8_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_a9 |

(@ 0x0000013C) Pad configuration register of port HIF_A9 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12136 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_a9_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_bhen |

(@ 0x000001A0) Pad configuration register of port HIF_BHEN (asic_ctrl_access_k y protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12536 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_bhen_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_csn |

(@ 0x000001A4) Pad configuration register of port HIF_CSN (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12552 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_csn_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d0 |

(@ 0x00000160) Pad configuration register of port HIF_D0 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12280 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d1 |

(@ 0x00000164) Pad configuration register of port HIF_D1 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12296 of file netx90_app.h.

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d10 |

(@ 0x00000188) Pad configuration register of port HIF_D10 (asic_ctrl_access_ke protected). Pad type: PRUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12440 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d10_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d11 |

(@ 0x0000018C) Pad configuration register of port HIF_D11 (asic_ctrl_access_ke protected). Pad type: PRUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12456 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d11_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d12 |

(@ 0x00000190) Pad configuration register of port HIF_D12 (asic_ctrl_access_ke protected). Pad type: PRUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12472 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d12_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d13 |

(@ 0x00000194) Pad configuration register of port HIF_D13 (asic_ctrl_access_ke protected). Pad type: PRUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12488 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d13_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d14 |

(@ 0x00000198) Pad configuration register of port HIF_D14 (asic_ctrl_access_ke protected). Pad type: PRUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12504 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d14_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d15 |

(@ 0x0000019C) Pad configuration register of port HIF_D15 (asic_ctrl_access_ke protected). Pad type: PRUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12520 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d15_b |

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d2 |

(@ 0x00000168) Pad configuration register of port HIF_D2 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12312 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d3 |

(@ 0x0000016C) Pad configuration register of port HIF_D3 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12328 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d4 |

(@ 0x00000170) Pad configuration register of port HIF_D4 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12344 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d4_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d5 |

(@ 0x00000174) Pad configuration register of port HIF_D5 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12360 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d5_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d6 |

(@ 0x00000178) Pad configuration register of port HIF_D6 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12376 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d6_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d7 |

(@ 0x0000017C) Pad configuration register of port HIF_D7 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12392 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d7_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d8 |

(@ 0x00000180) Pad configuration register of port HIF_D8 (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12408 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d8_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_d9 |

(@ 0x00000184) Pad configuration register of port HIF_D9 (asic_ctrl_access_key protected). Pad type: PRUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12424 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_d9_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_dirq |

(@ 0x000001B4) Pad configuration register of port HIF_DIRQ (asic_ctrl_access_k y protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12616 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_dirq_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_rdn |

(@ 0x000001A8) Pad configuration register of port HIF_RDN (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12568 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_rdn_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_rdy |

(@ 0x000001B0) Pad configuration register of port HIF_RDY (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12600 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_rdy_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_sdclk |

(@ 0x000001B8) Pad configuration register of port HIF_SDCLK (asic_ctrl_access_key protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12632 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_sdclk_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_hif_wrn |

(@ 0x000001AC) Pad configuration register of port HIF_WRN (asic_ctrl_access_ke protected). Pad type: PDUW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 12584 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_hif_wrn_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_col |

(@ 0x00000064) Pad configuration register of port MII0_COL (asic_ctrl_access_k y protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11280 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_col_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_col_bga2 |

(@ 0x000000C4) Pad configuration register of port MII0_COL_BGA2 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11661 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_col_bga2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_crs |

(@ 0x00000068) Pad configuration register of port MII0_CRS (asic_ctrl_access_k y protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11296 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_crs_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_crs_bga2 |

(@ 0x000000C8) Pad configuration register of port MII0_CRS_BGA2 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11677 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_crs_bga2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_rxclk |

(@ 0x00000030) Pad configuration register of port MII0_RXCLK (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11076 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_rxclk_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_rxd0 |

(@ 0x00000034) Pad configuration register of port MII0_RXD0 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11092 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_rxd0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_rxd1 |

(@ 0x00000038) Pad configuration register of port MII0_RXD1 (asic_ctrl_access_key protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11107 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_rxd1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_rxd2 |

(@ 0x0000003C) Pad configuration register of port MII0_RXD2 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11123 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_rxd2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_rxd3 |

(@ 0x00000040) Pad configuration register of port MII0_RXD3 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11139 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_rxd3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_rxdv |

(@ 0x00000044) Pad configuration register of port MII0_RXDV (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11154 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_rxdv_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_rxer |

(@ 0x00000048) Pad configuration register of port MII0_RXER (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11169 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_rxer_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_txclk |

(@ 0x0000004C) Pad configuration register of port MII0_TXCLK (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11184 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_txclk_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_txd0 |

(@ 0x00000050) Pad configuration register of port MII0_TXD0 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc2) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11200 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_txd0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_txd1 |

(@ 0x00000054) Pad configuration register of port MII0_TXD1 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc3) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11216 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_txd1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_txd2 |

(@ 0x00000058) Pad configuration register of port MII0_TXD2 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc2) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11232 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_txd2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_txd3 |

(@ 0x0000005C) Pad configuration register of port MII0_TXD3 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc3) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11248 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_txd3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_txen |

(@ 0x00000060) Pad configuration register of port MII0_TXEN (asic_ctrl_access_key protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11264 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_txen_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii0_txen_bga2 |

(@ 0x000000C0) Pad configuration register of port MII0_TXEN_BGA2 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11645 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii0_txen_bga2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_col |

(@ 0x000000A4) Pad configuration register of port MII1_COL (asic_ctrl_access_k y protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11533 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_col_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_col_bga2 |

(@ 0x000000D4) Pad configuration register of port MII1_COL_BGA2 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11722 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_col_bga2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_crs |

(@ 0x000000A8) Pad configuration register of port MII1_CRS (asic_ctrl_access_k y protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11549 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_crs_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_crs_bga2 |

(@ 0x000000D8) Pad configuration register of port MII1_CRS_BGA2 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11738 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_crs_bga2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_rxclk |

(@ 0x00000070) Pad configuration register of port MII1_RXCLK (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11328 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_rxclk_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_rxd0 |

(@ 0x00000074) Pad configuration register of port MII1_RXD0 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i_double_bond) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11344 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_rxd0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_rxd1 |

(@ 0x00000078) Pad configuration register of port MII1_RXD1 (asic_ctrl_access_key protected). Pad type: PDDW0408SCDG_33(double_bond) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11359 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_rxd1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_rxd2 |

(@ 0x0000007C) Pad configuration register of port MII1_RXD2 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33(double_bond) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11375 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_rxd2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_rxd3 |

(@ 0x00000080) Pad configuration register of port MII1_RXD3 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i_double_bond) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11391 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_rxd3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_rxdv |

(@ 0x00000084) Pad configuration register of port MII1_RXDV (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11406 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_rxdv_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_rxer |

(@ 0x00000088) Pad configuration register of port MII1_RXER (asic_ctrl_access_key protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11421 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_rxer_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_rxer_bga2 |

(@ 0x000000D0) Pad configuration register of port MII1_RXER_BGA2 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11707 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_rxer_bga2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_txclk |

(@ 0x0000008C) Pad configuration register of port MII1_TXCLK (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc2) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11437 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_txclk_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_txd0 |

(@ 0x00000090) Pad configuration register of port MII1_TXD0 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33(double_bond) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11453 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_txd0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_txd1 |

(@ 0x00000094) Pad configuration register of port MII1_TXD1 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33(double_bond) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11469 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_txd1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_txd2 |

(@ 0x00000098) Pad configuration register of port MII1_TXD2 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33(double_bond) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11485 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_txd2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_txd3 |

(@ 0x0000009C) Pad configuration register of port MII1_TXD3 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_33(double_bond) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11501 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_txd3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii1_txen |

(@ 0x000000A0) Pad configuration register of port MII1_TXEN (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc2) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11517 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii1_txen_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii_mdc |

(@ 0x000000B0) Pad configuration register of port MII_MDC (asic_ctrl_access_ke protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc2) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11581 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii_mdc_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mii_mdio |

(@ 0x000000B4) Pad configuration register of port MII_MDIO (asic_ctrl_access_k y protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc2) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11597 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mii_mdio_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mled0 |

(@ 0x00000008) Pad configuration register of port MLED0 (asic_ctrl_access_key protected). Pad type: PRDW0408CDG_33(o_sc) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 10927 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mled0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mled1 |

(@ 0x0000000C) Pad configuration register of port MLED1 (asic_ctrl_access_key protected). Pad type: PRDW0408CDG_33(o_sc) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 10941 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mled1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mled2 |

(@ 0x00000010) Pad configuration register of port MLED2 (asic_ctrl_access_key protected). Pad type: PRDW0408CDG_33(o) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 10955 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mled2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mled3 |

(@ 0x00000014) Pad configuration register of port MLED3 (asic_ctrl_access_key protected). Pad type: PRDW0408CDG_33(o) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 10969 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mled3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mmio0 |

(@ 0x000000E0) Pad configuration register of port MMIO0 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc2) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11768 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mmio0_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mmio1 |

(@ 0x000000E4) Pad configuration register of port MMIO1 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc2) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11784 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mmio1_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mmio2 |

(@ 0x000000E8) Pad configuration register of port MMIO2 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc3) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11800 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mmio2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mmio3 |

(@ 0x000000EC) Pad configuration register of port MMIO3 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_SW_33(adc3) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11816 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mmio3_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mmio4 |

(@ 0x000000F0) Pad configuration register of port MMIO4 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11832 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mmio4_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mmio5 |

(@ 0x000000F4) Pad configuration register of port MMIO5 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11848 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mmio5_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mmio6 |

(@ 0x000000F8) Pad configuration register of port MMIO6 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11864 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mmio6_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_mmio7 |

(@ 0x000000FC) Pad configuration register of port MMIO7 (asic_ctrl_access_key protected). Pad type: PRDW0408SCDG_ANA_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11880 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_mmio7_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_phy0_led_link_in |

(@ 0x0000006C) Pad configuration register of port PHY0_LED_LINK_IN (asic_ctrl_access_key protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11312 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_phy0_led_link_in_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_phy0_led_link_in_bga2 |

(@ 0x000000CC) Pad configuration register of port PHY0_LED_LINK_IN_BGA2 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11692 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_phy0_led_link_in_bga2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_phy1_led_link_in |

(@ 0x000000AC) Pad configuration register of port PHY1_LED_LINK_IN (asic_ctrl_access_key protected). Pad type: PDDW0408SCDG_33 For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11565 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_phy1_led_link_in_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_phy1_led_link_in_bga2 |

(@ 0x000000DC) Pad configuration register of port PHY1_LED_LINK_IN_BGA2 (asic_ctrl_access_key protected). Pad type: PDDW0204SCDG_33(i) For details refer to description of register pad_ctrl_rdy_n.

Definition at line 11753 of file netx90_app.h.

| struct { ... } pad_ctrl_Type::pad_ctrl_phy1_led_link_in_bga2_b |

| __IOM uint32_t pad_ctrl_Type::pad_ctrl_rdy_n |