|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

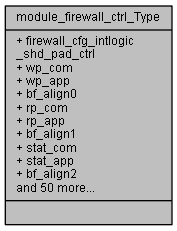

module_firewall_ctrl (module_firewall_ctrl) More...

#include <netx90_app.h>

module_firewall_ctrl (module_firewall_ctrl)

Definition at line 16862 of file netx90_app.h.

| union { ... } |

< (@ 0xFF401740) module_firewall_ctrl Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t module_firewall_ctrl_Type::abort_dis |

[31..31] disable abort-generation for denied accesses 1: no ERROR response for denied accesses (not recommended). 0: ERROR response for denied accesses (default)

[31..31] disable abort-generation for denied accesses

[31..31] Disable abort-generation for denied accesses for all registers controlled by this register.

Definition at line 16897 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::bf_align0 |

[3..2] bitField alignment value for aeabi compatibility

Definition at line 16882 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::bf_align1 |

[7..6] bitField alignment value for aeabi compatibility

Definition at line 16886 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::bf_align2 |

[30..10] bitField alignment value for aeabi compatibility

[11..10] bitField alignment value for aeabi compatibility

Definition at line 16896 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::bf_align3 |

[15..14] bitField alignment value for aeabi compatibility

Definition at line 17131 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::bf_align4 |

[19..18] bitField alignment value for aeabi compatibility

Definition at line 17136 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::bf_align5 |

[23..22] bitField alignment value for aeabi compatibility

Definition at line 17141 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::bf_align6 |

[27..26] bitField alignment value for aeabi compatibility

Definition at line 17146 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::bf_align7 |

[30..30] bitField alignment value for aeabi compatibility

Definition at line 17151 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::ext_rdy_cfg_wp_app |

[1..1] Write permission for APP side masters for the following register(s): hif_asyncmem_ctrl.ext_rdy_cfg

Definition at line 17112 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::ext_rdy_cfg_wp_com |

[0..0] Write permission for COM side masters for the following register(s): hif_asyncmem_ctrl.ext_rdy_cfg

Definition at line 17110 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::ext_rdy_status_wp_app |

[5..5] Write permission for APP side masters for the following register(s): hif_asyncmem_ctrl.ext_rdy_status

Definition at line 17117 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::ext_rdy_status_wp_com |

[4..4] Write permission for COM side masters for the following register(s): hif_asyncmem_ctrl.ext_rdy_status

Definition at line 17115 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::extsram0_ctrl_wp_app |

[9..9] Write permission for APP side masters for the following register(s): hif_asyncmem_ctrl.extsram0_ctrl and hif_asyncmem_ctrl.ext_cs _apm_ctr

Definition at line 17123 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::extsram0_ctrl_wp_com |

[8..8] Write permission for COM side masters for the following register(s): hif_asyncmem_ctrl.extsram0_ctrl and hif_asyncmem_ctrl.ext_cs _apm_ctr

Definition at line 17120 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::extsram1_ctrl_wp_app |

[13..13] Write permission for APP side masters for the following register(s): hif_asyncmem_ctrl.extsram1_ctrl

Definition at line 17129 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::extsram1_ctrl_wp_com |

[12..12] Write permission for COM side masters for the following register(s): hif_asyncmem_ctrl.extsram1_ctrl

Definition at line 17127 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::extsram2_ctrl_wp_app |

[17..17] Write permission for APP side masters for the following register(s): hif_asyncmem_ctrl.extsram2_ctrl

Definition at line 17134 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::extsram2_ctrl_wp_com |

[16..16] Write permission for COM side masters for the following register(s): hif_asyncmem_ctrl.extsram2_ctrl

Definition at line 17132 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::extsram3_ctrl_wp_app |

[21..21] Write permission for APP side masters for the following register(s): hif_asyncmem_ctrl.extsram3_ctrl

Definition at line 17139 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::extsram3_ctrl_wp_com |

[20..20] Write permission for COM side masters for the following register(s): hif_asyncmem_ctrl.extsram3_ctrl

Definition at line 17137 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_hifmemctrl |

(@ 0x0000003C) Firewall configuration register for the configuration registers of the HIF MI. See description of register firewall_cfg_intlogic_shd_pad_ctrl for details. Note that read access cannot be blocked for the configuration registers of the HIF MI. The failed-access-status is not logged individually for each MI configuration register. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_firew ll. The functionality of th

Definition at line 17097 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_hifmemctrl_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_ecc_ctrl |

(@ 0x0000000C) Firewall configuration register for the intlogic_shd_ecc_ctrl module. See description of register firewall_cfg_intlogic_ hd_pad_ctrl for details. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_fi ewall. The functionality of the status bits are not influenced by ASIC_CTRL_COM.netx_lock.lock_firewal

Definition at line 16952 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_ecc_ctrl_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc |

(@ 0x00000010) Firewall configuration register for the intlogic_shd_madc module. See description of register firewall_cfg_intlogic_ hd_pad_ctrl for details. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_fi ewall. The functionality of the status bits are not influenced by ASIC_CTRL_COM.netx_lock.lock_firewal

Definition at line 16976 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_seq0 |

(@ 0x00000014) Firewall configuration register for the intlogic_shd_madc_seq0 module. See description of register firewall_cfg_intlogic_ hd_pad_ctrl for details. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_fi ewall. The functionality of the status bits are not influenced by ASIC_CTRL_COM.netx_lock.lock_firewal

Definition at line 17000 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_seq0_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_seq1 |

(@ 0x00000018) Firewall configuration register for the intlogic_shd_madc_seq1 module. See description of register firewall_cfg_intlogic_ hd_pad_ctrl for details. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_fi ewall. The functionality of the status bits are not influenced by ASIC_CTRL_COM.netx_lock.lock_firewal

Definition at line 17024 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_seq1_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_seq2 |

(@ 0x0000001C) Firewall configuration register for the intlogic_shd_madc_seq2 module. See description of register firewall_cfg_intlogic_ hd_pad_ctrl for details. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_fi ewall. The functionality of the status bits are not influenced by ASIC_CTRL_COM.netx_lock.lock_firewal

Definition at line 17048 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_seq2_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_seq3 |

(@ 0x00000020) Firewall configuration register for the intlogic_shd_madc_seq3 module. See description of register firewall_cfg_intlogic_ hd_pad_ctrl for details. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_fi ewall. The functionality of the status bits are not influenced by ASIC_CTRL_COM.netx_lock.lock_firewal

Definition at line 17072 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_madc_seq3_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_pad_ctrl |

(@ 0x00000000) Firewall configuration register for the intlogic_shd_pad_ctrl module. Basic function: A denied access will generate an ERROR-response (abort). Masters which cannot handle aborts directly can generate an IRQ to their controlling master when they receive an abort (e.g. the DPM-master can generate an IRQ to its host or the DMA-controllers can generate an IRQ to the ARM-CPU). The firewall will no generate any IRQ by itself. A denied write access will be junked. A denied read access will return

Definition at line 16865 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_pad_ctrl_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_sqi |

(@ 0x00000004) Firewall configuration register for the intlogic_shd_sqi module. See description of register firewall_cfg_intlogic_ hd_pad_ctrl for details. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_fi ewall. The functionality of the status bits are not influenced by ASIC_CTRL_COM.netx_lock.lock_firewal

Definition at line 16904 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_sqi_b |

| __IOM uint32_t module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_uart |

(@ 0x00000008) Firewall configuration register for the intlogic_shd_uart module. See description of register firewall_cfg_intlogic_ hd_pad_ctrl for details. Note: The configuration bits of this register can be locked to protect it from reconfiguration by ASIC_CTRL_COM.netx_lock.lock_fi ewall. The functionality of the status bits are not influenced by ASIC_CTRL_COM.netx_lock.lock_firewal

Definition at line 16928 of file netx90_app.h.

| struct { ... } module_firewall_ctrl_Type::firewall_cfg_intlogic_shd_uart_b |

| __IM uint32_t module_firewall_ctrl_Type::RESERVED[6] |

Definition at line 17094 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::rp_app |

[5..5] read permission for APP side masters

Definition at line 16885 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::rp_com |

[4..4] read permission for COM side masters 1: permit read access 0: deny read access

[4..4] read permission for COM side masters

Definition at line 16883 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::sdram_ctrl_wp_app |

[25..25] Write permission for APP side masters for the following register(s): all registers of hif_sdram_ctrl and hifmem_priority_ctrl

Definition at line 17144 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::sdram_ctrl_wp_com |

[24..24] Write permission for COM side masters for the following register(s): all registers of hif_sdram_ctrl and hifmem_priority_ctrl

Definition at line 17142 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::stat_app |

[9..9] status for APP side masters, write '1' to clear.

[29..29] Status for APP side masters for all registers above, write '1' to clear.

Definition at line 16895 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::stat_com |

[8..8] Firewall status for COM side masters, write '1' to clear. 1: an access of the COM side was denied 0: no denied accesses Note: Clearing the stat-bit by software has lower priority than setting by hardware. I.e. clearing a status bit while an access of the related is denied, will fail. Ensure that no access will be denied before clearing by stopping accessing master (e.g. DMAC which could perform long jobs with long bursts).

[8..8] Firewall status for COM side masters, write '1' to clear.

[28..28] Firewall status for COM side masters for all registers above, write '1' to clear.

Definition at line 16887 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::wp_app |

[1..1] write permission for APP side masters

Definition at line 16881 of file netx90_app.h.

| __IOM uint32_t module_firewall_ctrl_Type::wp_com |

[0..0] write permission for COM side masters 1: permit write access 0: deny write access

[0..0] write permission for COM side masters

Definition at line 16879 of file netx90_app.h.