|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

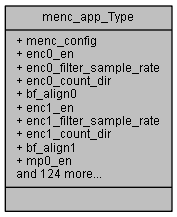

menc_app (menc_app) More...

#include <netx90_app.h>

Data Fields | |

| union { | |

| __IOM uint32_t menc_config | |

| struct { | |

| __IOM uint32_t enc0_en: 1 | |

| __IOM uint32_t enc0_filter_sample_rate: 3 | |

| __IOM uint32_t enc0_count_dir: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t enc1_en: 1 | |

| __IOM uint32_t enc1_filter_sample_rate: 3 | |

| __IOM uint32_t enc1_count_dir: 1 | |

| __IOM uint32_t bf_align1: 3 | |

| __IOM uint32_t mp0_en: 1 | |

| __IOM uint32_t mp0_filter_sample_rate: 3 | |

| __IOM uint32_t bf_align2: 4 | |

| __IOM uint32_t mp1_en: 1 | |

| __IOM uint32_t mp1_filter_sample_rate: 3 | |

| __IOM uint32_t bf_align3: 4 | |

| } menc_config_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_enc0_position | |

| struct { | |

| __IOM uint32_t val: 32 | |

| } menc_enc0_position_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_enc1_position | |

| struct { | |

| __IOM uint32_t val: 32 | |

| } menc_enc1_position_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_capture_now | |

| struct { | |

| __IOM uint32_t cap0_now: 1 | |

| __IOM uint32_t cap1_now: 1 | |

| __IOM uint32_t cap2_now: 1 | |

| __IOM uint32_t cap3_now: 1 | |

| __IOM uint32_t bf_align0: 28 | |

| } menc_capture_now_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_capture0_config | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t src: 3 | |

| __IOM uint32_t src_nr: 1 | |

| __IOM uint32_t conce: 1 | |

| __IOM uint32_t bf_align0: 10 | |

| } menc_capture0_config_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture0_val | |

| struct { | |

| __IM uint32_t val: 32 | |

| } menc_capture0_val_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture0_ta | |

| struct { | |

| __IM uint32_t val: 20 | |

| __IM uint32_t bf_align0: 12 | |

| } menc_capture0_ta_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture0_te | |

| struct { | |

| __IM uint32_t val: 20 | |

| __IM uint32_t bf_align0: 12 | |

| } menc_capture0_te_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_capture1_config | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t src: 3 | |

| __IOM uint32_t src_nr: 1 | |

| __IOM uint32_t conce: 1 | |

| __IOM uint32_t bf_align0: 10 | |

| } menc_capture1_config_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture1_val | |

| struct { | |

| __IM uint32_t val: 32 | |

| } menc_capture1_val_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture1_ta | |

| struct { | |

| __IM uint32_t val: 20 | |

| __IM uint32_t bf_align0: 12 | |

| } menc_capture1_ta_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture1_te | |

| struct { | |

| __IM uint32_t val: 20 | |

| __IM uint32_t bf_align0: 12 | |

| } menc_capture1_te_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_capture2_config | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t src: 3 | |

| __IOM uint32_t src_nr: 1 | |

| __IOM uint32_t conce: 1 | |

| __IOM uint32_t bf_align0: 10 | |

| } menc_capture2_config_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture2_val | |

| struct { | |

| __IM uint32_t val: 32 | |

| } menc_capture2_val_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture2_ta | |

| struct { | |

| __IM uint32_t val: 20 | |

| __IM uint32_t bf_align0: 12 | |

| } menc_capture2_ta_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture2_te | |

| struct { | |

| __IM uint32_t val: 20 | |

| __IM uint32_t bf_align0: 12 | |

| } menc_capture2_te_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_capture3_config | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t src: 3 | |

| __IOM uint32_t src_nr: 1 | |

| __IOM uint32_t conce: 1 | |

| __IOM uint32_t bf_align0: 10 | |

| } menc_capture3_config_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture3_val | |

| struct { | |

| __IM uint32_t val: 32 | |

| } menc_capture3_val_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture3_ta | |

| struct { | |

| __IM uint32_t val: 20 | |

| __IM uint32_t bf_align0: 12 | |

| } menc_capture3_ta_b | |

| }; | |

| union { | |

| __IM uint32_t menc_capture3_te | |

| struct { | |

| __IM uint32_t val: 20 | |

| __IM uint32_t bf_align0: 12 | |

| } menc_capture3_te_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_status | |

| struct { | |

| __IOM uint32_t enc0_edge: 1 | |

| __IOM uint32_t enc0_ovfl_pos: 1 | |

| __IOM uint32_t enc0_ovfl_neg: 1 | |

| __IOM uint32_t enc0_phase_error: 1 | |

| __IOM uint32_t enc0_n: 1 | |

| __IOM uint32_t bf_align0: 2 | |

| __IOM uint32_t enc0_dir_ro: 1 | |

| __IOM uint32_t enc1_edge: 1 | |

| __IOM uint32_t enc1_ovfl_pos: 1 | |

| __IOM uint32_t enc1_ovfl_neg: 1 | |

| __IOM uint32_t enc1_phase_error: 1 | |

| __IOM uint32_t enc1_n: 1 | |

| __IOM uint32_t bf_align1: 2 | |

| __IOM uint32_t enc1_dir_ro: 1 | |

| __IOM uint32_t cap0: 1 | |

| __IOM uint32_t cap1: 1 | |

| __IOM uint32_t cap2: 1 | |

| __IOM uint32_t cap3: 1 | |

| __IOM uint32_t bf_align2: 4 | |

| __IOM uint32_t mp0: 1 | |

| __IOM uint32_t mp1: 1 | |

| __IOM uint32_t bf_align3: 6 | |

| } menc_status_b | |

| }; | |

| union { | |

| __IM uint32_t menc_irq_masked | |

| struct { | |

| __IM uint32_t enc0_edge: 1 | |

| __IM uint32_t enc0_ovfl_pos: 1 | |

| __IM uint32_t enc0_ovfl_neg: 1 | |

| __IM uint32_t enc0_phase_error: 1 | |

| __IM uint32_t enc0_n: 1 | |

| __IM uint32_t bf_align0: 3 | |

| __IM uint32_t enc1_edge: 1 | |

| __IM uint32_t enc1_ovfl_pos: 1 | |

| __IM uint32_t enc1_ovfl_neg: 1 | |

| __IM uint32_t enc1_phase_error: 1 | |

| __IM uint32_t enc1_n: 1 | |

| __IM uint32_t bf_align1: 3 | |

| __IM uint32_t cap0: 1 | |

| __IM uint32_t cap1: 1 | |

| __IM uint32_t cap2: 1 | |

| __IM uint32_t cap3: 1 | |

| __IM uint32_t bf_align2: 4 | |

| __IM uint32_t mp0: 1 | |

| __IM uint32_t mp1: 1 | |

| __IM uint32_t bf_align3: 6 | |

| } menc_irq_masked_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_irq_msk_set | |

| struct { | |

| __IOM uint32_t enc0_edge: 1 | |

| __IOM uint32_t enc0_ovfl_pos: 1 | |

| __IOM uint32_t enc0_ovfl_neg: 1 | |

| __IOM uint32_t enc0_phase_error: 1 | |

| __IOM uint32_t enc0_n: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t enc1_edge: 1 | |

| __IOM uint32_t enc1_ovfl_pos: 1 | |

| __IOM uint32_t enc1_ovfl_neg: 1 | |

| __IOM uint32_t enc1_phase_error: 1 | |

| __IOM uint32_t enc1_n: 1 | |

| __IOM uint32_t bf_align1: 3 | |

| __IOM uint32_t cap0: 1 | |

| __IOM uint32_t cap1: 1 | |

| __IOM uint32_t cap2: 1 | |

| __IOM uint32_t cap3: 1 | |

| __IOM uint32_t bf_align2: 4 | |

| __IOM uint32_t mp0: 1 | |

| __IOM uint32_t mp1: 1 | |

| __IOM uint32_t bf_align3: 6 | |

| } menc_irq_msk_set_b | |

| }; | |

| union { | |

| __IOM uint32_t menc_irq_msk_reset | |

| struct { | |

| __IOM uint32_t enc0_edge: 1 | |

| __IOM uint32_t enc0_ovfl_pos: 1 | |

| __IOM uint32_t enc0_ovfl_neg: 1 | |

| __IOM uint32_t enc0_phase_error: 1 | |

| __IOM uint32_t enc0_n: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t enc1_edge: 1 | |

| __IOM uint32_t enc1_ovfl_pos: 1 | |

| __IOM uint32_t enc1_ovfl_neg: 1 | |

| __IOM uint32_t enc1_phase_error: 1 | |

| __IOM uint32_t enc1_n: 1 | |

| __IOM uint32_t bf_align1: 3 | |

| __IOM uint32_t cap0: 1 | |

| __IOM uint32_t cap1: 1 | |

| __IOM uint32_t cap2: 1 | |

| __IOM uint32_t cap3: 1 | |

| __IOM uint32_t bf_align2: 4 | |

| __IOM uint32_t mp0: 1 | |

| __IOM uint32_t mp1: 1 | |

| __IOM uint32_t bf_align3: 6 | |

| } menc_irq_msk_reset_b | |

| }; | |

menc_app (menc_app)

Definition at line 29030 of file netx90_app.h.

| union { ... } |

< (@ 0xFF802300) menc_app Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t menc_app_Type::bf_align0 |

[7..5] bitField alignment value for aeabi compatibility

[31..4] bitField alignment value for aeabi compatibility

[31..22] bitField alignment value for aeabi compatibility

[6..5] bitField alignment value for aeabi compatibility

Definition at line 29048 of file netx90_app.h.

| __IM uint32_t menc_app_Type::bf_align0 |

[31..20] bitField alignment value for aeabi compatibility

[7..5] bitField alignment value for aeabi compatibility

Definition at line 29162 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::bf_align1 |

[15..13] bitField alignment value for aeabi compatibility

[14..13] bitField alignment value for aeabi compatibility

Definition at line 29061 of file netx90_app.h.

| __IM uint32_t menc_app_Type::bf_align1 |

[15..13] bitField alignment value for aeabi compatibility

Definition at line 29361 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::bf_align2 |

[23..20] bitField alignment value for aeabi compatibility

Definition at line 29072 of file netx90_app.h.

| __IM uint32_t menc_app_Type::bf_align2 |

[23..20] bitField alignment value for aeabi compatibility

Definition at line 29366 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::bf_align3 |

[31..28] bitField alignment value for aeabi compatibility

[31..26] bitField alignment value for aeabi compatibility

Definition at line 29083 of file netx90_app.h.

| __IM uint32_t menc_app_Type::bf_align3 |

[31..26] bitField alignment value for aeabi compatibility

Definition at line 29369 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::cap0 |

[16..16] Captured register 0

Definition at line 29330 of file netx90_app.h.

| __IM uint32_t menc_app_Type::cap0 |

[16..16] Captured register 0

Definition at line 29362 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::cap0_now |

[0..0] Capture menc_capture0 now (by SW). Capture by writing 1 to this register, reset automatically.

Definition at line 29111 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::cap1 |

[17..17] Captured register 1

Definition at line 29331 of file netx90_app.h.

| __IM uint32_t menc_app_Type::cap1 |

[17..17] Captured register 1

Definition at line 29363 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::cap1_now |

[1..1] Capture menc_capture1 now (by SW). Capture by writing 1 to this register, reset automatically.

Definition at line 29113 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::cap2 |

[18..18] Captured register 2

Definition at line 29332 of file netx90_app.h.

| __IM uint32_t menc_app_Type::cap2 |

[18..18] Captured register 2

Definition at line 29364 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::cap2_now |

[2..2] Capture menc_capture2 now (by SW). Capture by writing 1 to this register, reset automatically.

Definition at line 29115 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::cap3 |

[19..19] Captured register 3

Definition at line 29333 of file netx90_app.h.

| __IM uint32_t menc_app_Type::cap3 |

[19..19] Captured register 3

Definition at line 29365 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::cap3_now |

[3..3] Capture menc_capture3 now (by SW). Capture by writing 1 to this register, reset automatically.

Definition at line 29117 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::conce |

[21..21] Capture once: 0: continuous capture: each event overwrites old capture register 1: capture once: capture only, if menc_status.cap0 = 0

Definition at line 29141 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_count_dir |

[4..4] Encoder0 count direction: 0: standard 1: inverted

Definition at line 29047 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_dir_ro |

[7..7] Encoder0 direction (read only)

Definition at line 29320 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_edge |

[0..0] Edge at Encoder 0 occurred (rising or falling of enc0_a or enc0_b)

Definition at line 29312 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc0_edge |

[0..0] Edge at Encoder 0 occurred (rising or falling of enc0_a or enc0_b)

Definition at line 29346 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_en |

[0..0] Encoder0 enable: 0: Disable interrupts based on encoder0 signals.

Definition at line 29036 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_filter_sample_rate |

[3..1] Encoder0 filter sample rate: { | 0: none - Filter is disabled. 1: 10 ns - pulses < 10ns will be blocked, pulses

20ns will pass. 2: 20 ns - pulses < 20ns will be blocked,

pulses > 40ns will pass. 3: 50 ns - pulses < 50ns will be blocked, pulses > 100ns will pass. 4: 100 ns - pulses < 100ns will be blocked, pulses > 200ns will pass. 5: 200 ns - pulses < 200ns will be blocked, pulses > 400ns will pass. 6: 500 ns - pulses < 500ns will be blocked, pulses

1us will pass. 7: 1 us - pulses <

Definition at line 29038 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_n |

[4..4] Rising edge at input enc0_n.

Definition at line 29318 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc0_n |

[4..4] Rising edge at input enc0_n.

Definition at line 29352 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_ovfl_neg |

[2..2] Encoder0 overflow negative

Definition at line 29315 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc0_ovfl_neg |

[2..2] Encoder0 overflow negative

Definition at line 29349 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_ovfl_pos |

[1..1] Encoder0 overflow positive

Definition at line 29314 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc0_ovfl_pos |

[1..1] Encoder0 overflow positive

Definition at line 29348 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc0_phase_error |

[3..3] Phase error at encoder 0: Encoder inputs changed 2 phases in 1 cycle, which leads to unknown position.

Definition at line 29316 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc0_phase_error |

[3..3] Phase error at encoder 0: Encoder inputs changed 2 phases in 1 cycle, which leads to unknown position.

Definition at line 29350 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_count_dir |

[12..12] Encoder1 count direction: 0: standard 1: inverted

Definition at line 29060 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_dir_ro |

[15..15] Encoder1 direction (read only)

Definition at line 29329 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_edge |

[8..8] Edge at Encoder 1 occurred (rising or falling of enc1_a or enc1_b)

Definition at line 29321 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc1_edge |

[8..8] Edge at Encoder 1 occurred (rising or falling of enc1_a or enc1_b)

Definition at line 29354 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_en |

[8..8] Encoder1 enable: 0: Disable interrupts based on encoder1 signals.

Definition at line 29049 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_filter_sample_rate |

[11..9] Encoder1 filter sample rate: { | 0: none - Filter is disabled. 1: 10 ns - pulses < 10ns will be blocked, pulses

20ns will pass. 2: 20 ns - pulses < 20ns will be blocked,

pulses > 40ns will pass. 3: 50 ns - pulses < 50ns will be blocked, pulses > 100ns will pass. 4: 100 ns - pulses < 100ns will be blocked, pulses > 200ns will pass. 5: 200 ns - pulses < 200ns will be blocked, pulses > 400ns will pass. 6: 500 ns - pulses < 500ns will be blocked, pulses

1us will pass. 7: 1 us - pulses <

Definition at line 29051 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_n |

[12..12] Rising edge at input enc1_n.

Definition at line 29327 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc1_n |

[12..12] Rising edge at input enc1_n.

Definition at line 29360 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_ovfl_neg |

[10..10] Encoder1 overflow negative

Definition at line 29324 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc1_ovfl_neg |

[10..10] Encoder1 overflow negative

Definition at line 29357 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_ovfl_pos |

[9..9] Encoder1 overflow positive

Definition at line 29323 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc1_ovfl_pos |

[9..9] Encoder1 overflow positive

Definition at line 29356 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::enc1_phase_error |

[11..11] Phase error at encoder 1: Encoder inputs changed 2 phases in 1 cycle, which leads to unknown position.

Definition at line 29325 of file netx90_app.h.

| __IM uint32_t menc_app_Type::enc1_phase_error |

[11..11] Phase error at encoder 1: Encoder inputs changed 2 phases in 1 cycle, which leads to unknown position.

Definition at line 29358 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::menc_capture0_config |

(@ 0x00000010) Capture unit 0 configuration register

Definition at line 29124 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture0_config_b |

| __IM uint32_t menc_app_Type::menc_capture0_ta |

(@ 0x00000018) Capture unit 0 Ta: This register is only used for debug purposes.

Definition at line 29157 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture0_ta_b |

| __IM uint32_t menc_app_Type::menc_capture0_te |

(@ 0x0000001C) Capture unit 0 Te This register is only used for debug purposes.

Definition at line 29167 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture0_te_b |

| __IM uint32_t menc_app_Type::menc_capture0_val |

(@ 0x00000014) Capture unit 0 captured value

Definition at line 29149 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture0_val_b |

| __IOM uint32_t menc_app_Type::menc_capture1_config |

(@ 0x00000020) Capture unit 1 configuration register

Definition at line 29177 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture1_config_b |

| __IM uint32_t menc_app_Type::menc_capture1_ta |

(@ 0x00000028) Capture unit 1 Ta: This register is only used for debug purposes.

Definition at line 29200 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture1_ta_b |

| __IM uint32_t menc_app_Type::menc_capture1_te |

(@ 0x0000002C) Capture unit 1 Te This register is only used for debug purposes.

Definition at line 29210 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture1_te_b |

| __IM uint32_t menc_app_Type::menc_capture1_val |

(@ 0x00000024) Capture unit 1 captured value

Definition at line 29192 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture1_val_b |

| __IOM uint32_t menc_app_Type::menc_capture2_config |

(@ 0x00000030) Capture unit 2 configuration register

Definition at line 29220 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture2_config_b |

| __IM uint32_t menc_app_Type::menc_capture2_ta |

(@ 0x00000038) Capture unit 2 Ta: This register is only used for debug purposes.

Definition at line 29243 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture2_ta_b |

| __IM uint32_t menc_app_Type::menc_capture2_te |

(@ 0x0000003C) Capture unit 2 Te This register is only used for debug purposes.

Definition at line 29253 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture2_te_b |

| __IM uint32_t menc_app_Type::menc_capture2_val |

(@ 0x00000034) Capture unit 2 captured value

Definition at line 29235 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture2_val_b |

| __IOM uint32_t menc_app_Type::menc_capture3_config |

(@ 0x00000040) Capture unit 3 configuration register

Definition at line 29263 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture3_config_b |

| __IM uint32_t menc_app_Type::menc_capture3_ta |

(@ 0x00000048) Capture unit 3 Ta: This register is only used for debug purposes.

Definition at line 29286 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture3_ta_b |

| __IM uint32_t menc_app_Type::menc_capture3_te |

(@ 0x0000004C) Capture unit 3 Te This register is only used for debug purposes.

Definition at line 29296 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture3_te_b |

| __IM uint32_t menc_app_Type::menc_capture3_val |

(@ 0x00000044) Capture unit 3 captured value

Definition at line 29278 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture3_val_b |

| __IOM uint32_t menc_app_Type::menc_capture_now |

(@ 0x0000000C) Capture now register: This register allows activating the capture event by software for all 4 capture units.

Definition at line 29106 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_capture_now_b |

| __IOM uint32_t menc_app_Type::menc_config |

(@ 0x00000000) Encoder configuration register

Definition at line 29033 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_config_b |

| __IOM uint32_t menc_app_Type::menc_enc0_position |

(@ 0x00000004) Position of encoder 0

Definition at line 29088 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_enc0_position_b |

| __IOM uint32_t menc_app_Type::menc_enc1_position |

(@ 0x00000008) Position of encoder 1

Definition at line 29097 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_enc1_position_b |

| __IM uint32_t menc_app_Type::menc_irq_masked |

(@ 0x00000054) Masked IRQ register: Shows status of masked IRQs (as connected to ARM/xPIC).

Definition at line 29342 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_irq_masked_b |

| __IOM uint32_t menc_app_Type::menc_irq_msk_reset |

(@ 0x0000005C) IRQ mask disable: This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 29415 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_irq_msk_reset_b |

| __IOM uint32_t menc_app_Type::menc_irq_msk_set |

(@ 0x00000058) IRQ mask enable: The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating interrupt mask, delete old pending interrupts by writing the same value to adr_menc_status

Definition at line 29374 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_irq_msk_set_b |

| __IOM uint32_t menc_app_Type::menc_status |

(@ 0x00000050) Position and capture status: This register includes all raw IRQs and encoder direction. To reset an IRQ, write 1 to appropriate bit (except enc?_dir_ro).

Definition at line 29306 of file netx90_app.h.

| struct { ... } menc_app_Type::menc_status_b |

| __IOM uint32_t menc_app_Type::mp0 |

[24..24] Rising edge at Measurement Point 0

Definition at line 29335 of file netx90_app.h.

| __IM uint32_t menc_app_Type::mp0 |

[24..24] Rising edge at Measurement Point 0

Definition at line 29367 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::mp0_en |

[16..16] mp0 enable: 0: Disable interrupts based on mp0 signal.

Definition at line 29062 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::mp0_filter_sample_rate |

[19..17] Filter sample rate for mp0 signal: { | 0: none - Filter is disabled. 1: 10 ns - pulses < 10ns will be blocked, pulses > 20ns will pass. 2: 20 ns - pulses < 20ns will be blocked, pulses > 40ns will pass. 3: 50 ns - pulses < 50ns will be blocked, pulses > 100ns will pass. 4: 100 ns - pulses < 100ns will be blocked, pulses > 200ns will pass. 5: 200 ns - pulses < 200ns will be blocked, pulses

400ns will pass. 6: 500 ns - pulses < 500ns will be blocked,

pulses > 1us will pass. 7: 1 us - pul

Definition at line 29063 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::mp1 |

[25..25] Rising edge at Measurement Point 1

Definition at line 29336 of file netx90_app.h.

| __IM uint32_t menc_app_Type::mp1 |

[25..25] Rising edge at Measurement Point 1

Definition at line 29368 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::mp1_en |

[24..24] mp1 enable: 0: Disable interrupts based on mp1 signal.

Definition at line 29073 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::mp1_filter_sample_rate |

[27..25] Filter sample rate for mp1 signal: { | 0: none - Filter is disabled. 1: 10 ns - pulses < 10ns will be blocked, pulses > 20ns will pass. 2: 20 ns - pulses < 20ns will be blocked, pulses > 40ns will pass. 3: 50 ns - pulses < 50ns will be blocked, pulses > 100ns will pass. 4: 100 ns - pulses < 100ns will be blocked, pulses > 200ns will pass. 5: 200 ns - pulses < 200ns will be blocked, pulses

400ns will pass. 6: 500 ns - pulses < 500ns will be blocked,

pulses > 1us will pass. 7: 1 us - pul

Definition at line 29074 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::src |

[19..17] Capture source (what to capture): 0: system time ns (independent of src_nr) 1: position channel 0/1 2: Ta of channel 0/1 3: Te of channel 0/1 4: Ta+Te of channel 0/1 5: period in clock cycles (independent of src_nr)

[19..17] Capture source (what to capture): s. capture0_config-src

Definition at line 29135 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::src_nr |

[20..20] Capture source channel: 0: encoder/channel 0 1: encoder/channel 1

Definition at line 29139 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::trigger |

[16..0] Capture start signal: 0x0...0x0FFFF: start at (ECNT == trigger) 0x10000: positive edge of enc0_n 0x10001: negative edge of enc0_n 0x10002: positive edge of enc1_n 0x10003: positive edge of enc1_n 0x10004: any edge of enc0_a or enc0_b 0x10005: any edge of enc1_a or enc0_b 0x10006: positive edge of mp0 0x10007: negative edge of mp0 0x10008: positive edge of mp1 0x10009: negative edge of mp1 0x1000a: GPIO_APP_COUNTER0 = 0 0x1000b: GPIO_AP

[16..0] Capture start signal: s. capture0_config-trigger

Definition at line 29127 of file netx90_app.h.

| __IOM uint32_t menc_app_Type::val |

[31..0] Actual position of encoder 0. This register is writable but can also be changed by hardware.

[31..0] Actual position of encoder 1. This register is writable but can also be changed by hardware.

Definition at line 29091 of file netx90_app.h.

| __IM uint32_t menc_app_Type::val |

[31..0] Captured value

[19..0] Actual Ta: Time before first encoder pulse in period.

[19..0] Actual Te: Time after last encoder pulse in period.

Definition at line 29152 of file netx90_app.h.