|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

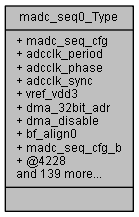

madc_seq0 (madc_seq0) More...

#include <netx90_app.h>

Data Fields | |

| union { | |

| __IOM uint32_t madc_seq_cfg | |

| struct { | |

| __IOM uint32_t adcclk_period: 8 | |

| __IOM uint32_t adcclk_phase: 8 | |

| __IOM uint32_t adcclk_sync: 1 | |

| __IOM uint32_t vref_vdd3: 1 | |

| __IOM uint32_t dma_32bit_adr: 1 | |

| __IOM uint32_t dma_disable: 1 | |

| __IOM uint32_t bf_align0: 12 | |

| } madc_seq_cfg_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_tracking_time_mux0 | |

| struct { | |

| __IOM uint32_t tt_add: 8 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_tracking_time_mux0_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_tracking_time_mux1 | |

| struct { | |

| __IOM uint32_t tt_add: 8 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_tracking_time_mux1_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_tracking_time_mux2 | |

| struct { | |

| __IOM uint32_t tt_add: 8 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_tracking_time_mux2_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_tracking_time_mux3 | |

| struct { | |

| __IOM uint32_t tt_add: 8 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_tracking_time_mux3_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_tracking_time_mux4 | |

| struct { | |

| __IOM uint32_t tt_add: 8 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_tracking_time_mux4_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_tracking_time_mux5 | |

| struct { | |

| __IOM uint32_t tt_add: 8 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_tracking_time_mux5_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_tracking_time_mux6 | |

| struct { | |

| __IOM uint32_t tt_add: 8 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_tracking_time_mux6_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_tracking_time_mux7 | |

| struct { | |

| __IOM uint32_t tt_add: 8 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_tracking_time_mux7_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_ms_en | |

| struct { | |

| __IOM uint32_t m0: 1 | |

| __IOM uint32_t m1: 1 | |

| __IOM uint32_t m2: 1 | |

| __IOM uint32_t m3: 1 | |

| __IOM uint32_t m4: 1 | |

| __IOM uint32_t m5: 1 | |

| __IOM uint32_t m6: 1 | |

| __IOM uint32_t m7: 1 | |

| __IOM uint32_t bf_align0: 24 | |

| } madc_seq_ms_en_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_ms_baseadr | |

| struct { | |

| __IOM uint32_t bf_align0: 1 | |

| __IOM uint32_t adr: 31 | |

| } madc_seq_ms_baseadr_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_m0 | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t oversample: 3 | |

| __IOM uint32_t mux: 3 | |

| __IOM uint32_t adr_offset: 5 | |

| __IOM uint32_t bf_align0: 4 | |

| } madc_seq_m0_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_m1 | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t oversample: 3 | |

| __IOM uint32_t mux: 3 | |

| __IOM uint32_t adr_offset: 5 | |

| __IOM uint32_t bf_align0: 4 | |

| } madc_seq_m1_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_m2 | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t oversample: 3 | |

| __IOM uint32_t mux: 3 | |

| __IOM uint32_t adr_offset: 5 | |

| __IOM uint32_t bf_align0: 4 | |

| } madc_seq_m2_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_m3 | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t oversample: 3 | |

| __IOM uint32_t mux: 3 | |

| __IOM uint32_t adr_offset: 5 | |

| __IOM uint32_t bf_align0: 4 | |

| } madc_seq_m3_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_m4 | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t oversample: 3 | |

| __IOM uint32_t mux: 3 | |

| __IOM uint32_t adr_offset: 5 | |

| __IOM uint32_t bf_align0: 4 | |

| } madc_seq_m4_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_m5 | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t oversample: 3 | |

| __IOM uint32_t mux: 3 | |

| __IOM uint32_t adr_offset: 5 | |

| __IOM uint32_t bf_align0: 4 | |

| } madc_seq_m5_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_m6 | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t oversample: 3 | |

| __IOM uint32_t mux: 3 | |

| __IOM uint32_t adr_offset: 5 | |

| __IOM uint32_t bf_align0: 4 | |

| } madc_seq_m6_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_m7 | |

| struct { | |

| __IOM uint32_t trigger: 17 | |

| __IOM uint32_t oversample: 3 | |

| __IOM uint32_t mux: 3 | |

| __IOM uint32_t adr_offset: 5 | |

| __IOM uint32_t bf_align0: 4 | |

| } madc_seq_m7_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_cmd | |

| struct { | |

| __IOM uint32_t run: 1 | |

| __IOM uint32_t continuous: 1 | |

| __IOM uint32_t reset: 1 | |

| __IOM uint32_t debug: 1 | |

| __IOM uint32_t bf_align0: 28 | |

| } madc_seq_cmd_b | |

| }; | |

| union { | |

| __IM uint32_t madc_seq_status | |

| struct { | |

| __IM uint32_t m_nr: 4 | |

| __IM uint32_t adc_half_clock_cycle: 5 | |

| __IM uint32_t bf_align0: 23 | |

| } madc_seq_status_b | |

| }; | |

| union { | |

| __IM uint32_t madc_seq_result_current | |

| struct { | |

| __IM uint32_t val: 15 | |

| __IM uint32_t bf_align0: 1 | |

| __IM uint32_t mnr: 3 | |

| __IM uint32_t bf_align1: 12 | |

| __IM uint32_t valid: 1 | |

| } madc_seq_result_current_b | |

| }; | |

| union { | |

| __IM uint32_t madc_seq_result_last | |

| struct { | |

| __IM uint32_t val: 15 | |

| __IM uint32_t bf_align0: 1 | |

| __IM uint32_t mnr: 3 | |

| __IM uint32_t bf_align1: 12 | |

| __IM uint32_t valid: 1 | |

| } madc_seq_result_last_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_debug | |

| struct { | |

| __IOM uint32_t adc_clk: 1 | |

| __IOM uint32_t adc_soc: 1 | |

| __IOM uint32_t adc_set_mux0: 1 | |

| __IOM uint32_t adc_set_mux1: 1 | |

| __IOM uint32_t adc_set_mux2: 1 | |

| __IOM uint32_t adc_set_mux3: 1 | |

| __IOM uint32_t adc_set_mux4: 1 | |

| __IOM uint32_t adc_set_mux5: 1 | |

| __IOM uint32_t adc_set_mux6: 1 | |

| __IOM uint32_t adc_set_mux7: 1 | |

| __IOM uint32_t bf_align0: 22 | |

| } madc_seq_debug_b | |

| }; | |

| __IM uint32_t | RESERVED [4] |

| union { | |

| __IOM uint32_t madc_seq_irq_raw | |

| struct { | |

| __IOM uint32_t m0_cmpl: 1 | |

| __IOM uint32_t m1_cmpl: 1 | |

| __IOM uint32_t m2_cmpl: 1 | |

| __IOM uint32_t m3_cmpl: 1 | |

| __IOM uint32_t m4_cmpl: 1 | |

| __IOM uint32_t m5_cmpl: 1 | |

| __IOM uint32_t m6_cmpl: 1 | |

| __IOM uint32_t m7_cmpl: 1 | |

| __IOM uint32_t seq_cmpl: 1 | |

| __IOM uint32_t dma_overrun: 1 | |

| __IOM uint32_t dma_hresp: 1 | |

| __IOM uint32_t bf_align0: 21 | |

| } madc_seq_irq_raw_b | |

| }; | |

| union { | |

| __IM uint32_t madc_seq_irq_masked | |

| struct { | |

| __IM uint32_t m0_cmpl: 1 | |

| __IM uint32_t m1_cmpl: 1 | |

| __IM uint32_t m2_cmpl: 1 | |

| __IM uint32_t m3_cmpl: 1 | |

| __IM uint32_t m4_cmpl: 1 | |

| __IM uint32_t m5_cmpl: 1 | |

| __IM uint32_t m6_cmpl: 1 | |

| __IM uint32_t m7_cmpl: 1 | |

| __IM uint32_t seq_cmpl: 1 | |

| __IM uint32_t dma_overrun: 1 | |

| __IM uint32_t dma_hresp: 1 | |

| __IM uint32_t bf_align0: 21 | |

| } madc_seq_irq_masked_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_irq_mask_set | |

| struct { | |

| __IOM uint32_t m0_cmpl: 1 | |

| __IOM uint32_t m1_cmpl: 1 | |

| __IOM uint32_t m2_cmpl: 1 | |

| __IOM uint32_t m3_cmpl: 1 | |

| __IOM uint32_t m4_cmpl: 1 | |

| __IOM uint32_t m5_cmpl: 1 | |

| __IOM uint32_t m6_cmpl: 1 | |

| __IOM uint32_t m7_cmpl: 1 | |

| __IOM uint32_t seq_cmpl: 1 | |

| __IOM uint32_t dma_overrun: 1 | |

| __IOM uint32_t dma_hresp: 1 | |

| __IOM uint32_t bf_align0: 21 | |

| } madc_seq_irq_mask_set_b | |

| }; | |

| union { | |

| __IOM uint32_t madc_seq_irq_mask_reset | |

| struct { | |

| __IOM uint32_t m0_cmpl: 1 | |

| __IOM uint32_t m1_cmpl: 1 | |

| __IOM uint32_t m2_cmpl: 1 | |

| __IOM uint32_t m3_cmpl: 1 | |

| __IOM uint32_t m4_cmpl: 1 | |

| __IOM uint32_t m5_cmpl: 1 | |

| __IOM uint32_t m6_cmpl: 1 | |

| __IOM uint32_t m7_cmpl: 1 | |

| __IOM uint32_t seq_cmpl: 1 | |

| __IOM uint32_t dma_overrun: 1 | |

| __IOM uint32_t dma_hresp: 1 | |

| __IOM uint32_t bf_align0: 21 | |

| } madc_seq_irq_mask_reset_b | |

| }; | |

madc_seq0 (madc_seq0)

Definition at line 17397 of file netx90_app.h.

| union { ... } |

< (@ 0xFF401800) madc_seq0 Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t madc_seq0_Type::adc_clk |

[0..0] ADC0 is sampling data.

Definition at line 17775 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::adc_half_clock_cycle |

[8..4] 0..30: current adcclk half clock cycle, 0 when adc is idle

Definition at line 17733 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_set_mux0 |

[2..2] ADC0_SET_MUX0 signal

Definition at line 17777 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_set_mux1 |

[3..3] ADC0_SET_MUX1 signal

Definition at line 17778 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_set_mux2 |

[4..4] ADC0_SET_MUX2 signal

Definition at line 17779 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_set_mux3 |

[5..5] ADC0_SET_MUX3 signal

Definition at line 17780 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_set_mux4 |

[6..6] ADC0_SET_MUX4 signal

Definition at line 17781 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_set_mux5 |

[7..7] ADC0_SET_MUX5 signal

Definition at line 17782 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_set_mux6 |

[8..8] ADC0_SET_MUX6 signal

Definition at line 17783 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_set_mux7 |

[9..9] ADC0_SET_MUX7 signal

Definition at line 17784 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adc_soc |

[1..1] ADC0_SOC signal

Definition at line 17776 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adcclk_period |

[7..0] Duration of an adcclk period in system clock cycles-1 For odd values the high phase of adcclk is one system clock cycle longer than the low phase.

Definition at line 17403 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adcclk_phase |

[15..8] Generation of the rising edge of the adcclk is delayed until the global clk_phase counter matches this value. NOTE: The rising edge of the adcclk ending the first sample period of a triggered measurement is NEVER delayed.

Definition at line 17406 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adcclk_sync |

[16..16] 0: The rising edges of adcclk are generated independently of the other ADCs. 1: Use adc_clock_phase for defined clock phases in relation to other ADC sequencers

Definition at line 17410 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adr |

[31..1] word (16 bit) aligned address, LSB is ignored In case of madc_seq_cfg-dma_32bit_adr=1, bit 1 will be ignored.

Definition at line 17558 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::adr_offset |

[27..23] Address offset specified in 16 bit words where the sum will be stored In case of madc_seq_cfg-dma_32bit_adr=1, this value will be interpreted as 32-bit address.

[27..23] Address offset specified in 16 bit words where the sum will be stored

Definition at line 17592 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::bf_align0 |

[31..20] bitField alignment value for aeabi compatibility

[31..8] bitField alignment value for aeabi compatibility

[0..0] bitField alignment value for aeabi compatibility

[31..28] bitField alignment value for aeabi compatibility

[31..4] bitField alignment value for aeabi compatibility

[31..10] bitField alignment value for aeabi compatibility

[31..11] bitField alignment value for aeabi compatibility

Definition at line 17424 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::bf_align0 |

[31..9] bitField alignment value for aeabi compatibility

[15..15] bitField alignment value for aeabi compatibility

[31..11] bitField alignment value for aeabi compatibility

Definition at line 17735 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::bf_align1 |

[30..19] bitField alignment value for aeabi compatibility

Definition at line 17746 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::continuous |

[1..1] Continuous mode: 0: run starts single conversion. All measurements enabled in madc_m_en are executed once. 1: start continuous conversion. All measurments enabled are executed repeatedly until stopped by resetting the run bit.

Definition at line 17709 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::debug |

[3..3] Debug mode: 0: ADC is controlled by measurement sequencer 1: ADC is directly controlled by madc_seq_debug register.

Definition at line 17720 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::dma_32bit_adr |

[18..18] The DMA engine only uses 32bit addresses and DWord access. This mode wastes memory but speeds up the DMA access by not running read-modify-write cycles.

Definition at line 17417 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::dma_disable |

[19..19] Disable DMA 1: DMA is disabled, results are not written to memory, only the current result will be visible in madc_seq_result_cur ent. 0: DMA is enabled, results are written to memory as defined in madc_seq_ms_adr and madc_seq_m*-adr_offset.

Definition at line 17420 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::dma_hresp |

[10..10] AHBL hresp signal received

Definition at line 17811 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::dma_hresp |

[10..10] AHBL hresp signal received

Definition at line 17832 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::dma_overrun |

[9..9] AHBL write buffer overrun result not written due to AHBL busy

Definition at line 17809 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::dma_overrun |

[9..9] AHBL write buffer overrun result not written due to AHBL busy

Definition at line 17830 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m0 |

[0..0] 1: Enable measurement defined by madc_seq_m0 for the current measurement sequence

Definition at line 17533 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m0_cmpl |

[0..0] event: measurement 0 completed

Definition at line 17800 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m0_cmpl |

[0..0] event: measurement 0 completed

Definition at line 17821 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m1 |

[1..1] 1: Enable measurement defined by madc_seq_m1 for the current measurement sequence

Definition at line 17535 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m1_cmpl |

[1..1] event: measurement 1 completed

Definition at line 17801 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m1_cmpl |

[1..1] event: measurement 1 completed

Definition at line 17822 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m2 |

[2..2] 1: Enable measurement defined by madc_seq_m2 for the current measurement sequence

Definition at line 17537 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m2_cmpl |

[2..2] event: measurement 2 completed

Definition at line 17802 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m2_cmpl |

[2..2] event: measurement 2 completed

Definition at line 17823 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m3 |

[3..3] 1: Enable measurement defined by madc_seq_m3 for the current measurement sequence

Definition at line 17539 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m3_cmpl |

[3..3] event: measurement 3 completed

Definition at line 17803 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m3_cmpl |

[3..3] event: measurement 3 completed

Definition at line 17824 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m4 |

[4..4] 1: Enable measurement defined by madc_seq_m4 for the current measurement sequence

Definition at line 17541 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m4_cmpl |

[4..4] event: measurement 4 completed

Definition at line 17804 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m4_cmpl |

[4..4] event: measurement 4 completed

Definition at line 17825 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m5 |

[5..5] 1: Enable measurement defined by madc_seq_m5 for the current measurement sequence

Definition at line 17543 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m5_cmpl |

[5..5] event: measurement 5 completed

Definition at line 17805 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m5_cmpl |

[5..5] event: measurement 5 completed

Definition at line 17826 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m6 |

[6..6] 1: Enable measurement defined by madc_seq_m6 for the current measurement sequence

Definition at line 17545 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m6_cmpl |

[6..6] event: measurement 6 completed

Definition at line 17806 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m6_cmpl |

[6..6] event: measurement 6 completed

Definition at line 17827 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m7 |

[7..7] 1: Enable measurement defined by madc_seq_m7 for the current measurement sequence

Definition at line 17547 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::m7_cmpl |

[7..7] event: measurement 7 completed

Definition at line 17807 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m7_cmpl |

[7..7] event: measurement 7 completed

Definition at line 17828 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::m_nr |

[3..0] Number of measurement configuration: 0..7: currently active measurement configuration, 8 when the ADC is idle

Definition at line 17731 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::madc_seq_cfg |

(@ 0x00000000) ADC static configuration

Definition at line 17400 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_cfg_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_cmd |

(@ 0x0000004C) Command Register: Run or abort processing the measurement sequence. This register is writable but can also be changed by hardware (reset).

Definition at line 17698 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_cmd_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_debug |

(@ 0x0000005C) Debug Mode register: If cmd-debug is enabled, this register directly controls inputs of both ADCs. Output data of both ADCs will still be at data0 and data1. In debug mode, a software reset (cfg-reset_n) will not influence these values (only directly signal ADC_NRES).

Definition at line 17766 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_debug_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_irq_mask_reset |

(@ 0x0000007C) IRQ disable mask: This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows bit number of the lowest active bit in IRQ_MASKED or MAX+1 when no bit is set.

Definition at line 17868 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_irq_mask_reset_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_irq_mask_set |

(@ 0x00000078) IRQ enable mask: The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating interrupt mask, delete old pending interrupts by writing the same value to adr_mpwm_irq_raw.

Definition at line 17838 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_irq_mask_set_b |

| __IM uint32_t madc_seq0_Type::madc_seq_irq_masked |

(@ 0x00000074) Masked IRQ: Shows status of masked IRQs (as connected to ARM/xPIC).

Definition at line 17817 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_irq_masked_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_irq_raw |

(@ 0x00000070) Raw IRQ: Read access shows status of unmasked IRQs. IRQs are set automatically and reset by writing to this register: Write access with '1' resets the appropriate IRQ (if event irq, reset status irqs at their source). Write access with '0' does not influence this bit.

Definition at line 17791 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_irq_raw_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_m0 |

(@ 0x0000002C) Measurement 0 configuration: A measurement performs (oversample+1) ADC conversions, summing up the results. Every ADC conversion starts with two adcclk periods followed by a sampling phase extension with a minimal duration selected by sext_sel. The sampling phase of the first ADC conversion of the measurement ends when the trigger condition is fulfilled. All subsequent conversions of the measurement do not wait for any trigger condition. The sum consisting of (oversample+1) ADC conversions i

Definition at line 17564 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_m0_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_m1 |

(@ 0x00000030) Measurement 1 configuration: s. madc_seq_m0 for details

Definition at line 17600 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_m1_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_m2 |

(@ 0x00000034) Measurement 2 configuration: s. madc_seq_m0 for details

Definition at line 17614 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_m2_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_m3 |

(@ 0x00000038) Measurement 3 configuration: s. madc_seq_m0 for details

Definition at line 17628 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_m3_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_m4 |

(@ 0x0000003C) Measurement 4 configuration: s. madc_seq_m0 for details

Definition at line 17642 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_m4_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_m5 |

(@ 0x00000040) Measurement 5 configuration: s. madc_seq_m0 for details

Definition at line 17656 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_m5_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_m6 |

(@ 0x00000044) Measurement 6 configuration: s. madc_seq_m0 for details

Definition at line 17670 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_m6_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_m7 |

(@ 0x00000048) Measurement 7 configuration: s. madc_seq_m0 for details

Definition at line 17684 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_m7_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_ms_baseadr |

(@ 0x00000028) Base address for writing the measurement results.

Definition at line 17554 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_ms_baseadr_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_ms_en |

(@ 0x00000024) Enable measurement configurations: Terminology: A measurement sequence consists of upto 8 measurements. A measurement consists of up to 8 samples. A sample needs at least 14 adcclk cycles (+ tracking time addon). This register enables the measurements belonging to a measurement sequence (up to 8). With the start of a measurement sequence (s. madc_seq_cmd) all sequence configuration registers (ms_en, ms_adr, m0..m7) are copied to shadow registers that can no longer be changed until the me

Definition at line 17519 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_ms_en_b |

| __IM uint32_t madc_seq0_Type::madc_seq_result_current |

(@ 0x00000054) Result register of current measurement

Definition at line 17740 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_result_current_b |

| __IM uint32_t madc_seq0_Type::madc_seq_result_last |

(@ 0x00000058) Result register of last measurement

Definition at line 17753 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_result_last_b |

| __IM uint32_t madc_seq0_Type::madc_seq_status |

(@ 0x00000050) Status of the current measurement sequence in progress

Definition at line 17727 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_status_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_tracking_time_mux0 |

(@ 0x00000004) ADC sample extension for input channel 0 Length of 2nd adcclk in steps of 10ns system clock(~ delay of 3rd adcclk edge). The capacitor inside ADC needs time to be charged depending on the driving strength of the external signal. For 12 bit precision, this time should be 9*(Rint+Rext)*C, with Rint=1kOhm and C=7.5pF. The total formula for this value is: tt_add = ceil((6,75 x Rext/kOhm)

Definition at line 17429 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_tracking_time_mux0_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_tracking_time_mux1 |

(@ 0x00000008) ADC sample extension for input channel 1 s. madc_seq_tracking_t me_mux0 for details.

Definition at line 17449 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_tracking_time_mux1_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_tracking_time_mux2 |

(@ 0x0000000C) ADC sample extension for input channel 2 s. madc_seq_tracking_t me_mux0 for details.

Definition at line 17459 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_tracking_time_mux2_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_tracking_time_mux3 |

(@ 0x00000010) ADC sample extension for input channel 3 s. madc_seq_tracking_t me_mux0 for details.

Definition at line 17469 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_tracking_time_mux3_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_tracking_time_mux4 |

(@ 0x00000014) ADC sample extension for input channel 4 s. madc_seq_tracking_t me_mux0 for details.

Definition at line 17479 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_tracking_time_mux4_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_tracking_time_mux5 |

(@ 0x00000018) ADC sample extension for input channel 5 s. madc_seq_tracking_t me_mux0 for details.

Definition at line 17489 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_tracking_time_mux5_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_tracking_time_mux6 |

(@ 0x0000001C) ADC sample extension for input channel 6 s. madc_seq_tracking_t me_mux0 for details.

Definition at line 17499 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_tracking_time_mux6_b |

| __IOM uint32_t madc_seq0_Type::madc_seq_tracking_time_mux7 |

(@ 0x00000020) ADC sample extension for input channel 7 s. madc_seq_tracking_t me_mux0 for details.

Definition at line 17509 of file netx90_app.h.

| struct { ... } madc_seq0_Type::madc_seq_tracking_time_mux7_b |

| __IM uint32_t madc_seq0_Type::mnr |

[18..16] number of measurement configuration

Definition at line 17745 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::mux |

[22..20] Input channel multiplexer setting The input multiplexer will always be set 1 system clock (10ns) before SOF. It will be reset after sampling to ensure a not-connected phase at the one-hot-coded multiplexer switches.

[22..20] Input channel multiplexer setting

Definition at line 17588 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::oversample |

[19..17] Number of samples minus one to sum for this measurement i.e. 0:sum 1 samples, 1:sum 2 samples, ...

[19..17] Number of samples minus one to sum for this measurement

Definition at line 17586 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::RESERVED[4] |

Definition at line 17788 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::reset |

[2..2] Reset this ADC-sequencer: In comparision to madc_adc01_static_cfg-adc01 reset_n, which resets a pair of ADC channels (e.g. ADC0 and ADC1), this bit only resets this single ADC-sequencer. The analog part of ADC will not be reset, but all registers of the controller (including result registers, which will not be reset in case of run=stop).

Definition at line 17714 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::run |

[0..0] Run bit: This bit can be set here or at madc_start to start all ADCs simultaneously. This bit can be reset here or automatically by hardware, when measurement sequence is finished. 1 : start measurement sequence. 0 : stop measurement sequence. Any conversion in progress is aborted and ADC returns to idle state with adcclk=0 and adc_soc=0.

Definition at line 17703 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::seq_cmpl |

[8..8] measurement sequence completed

Definition at line 17808 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::seq_cmpl |

[8..8] measurement sequence completed

Definition at line 17829 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::trigger |

[16..0] Trigger condition for measurement 0x0...0x0FFFF: condition (ECNT == trigger) 0x10000...0x10005: delayed DTEVT[0..5]==1 0x10006: GPIO_APP_COUNTER0 = 0 0x10007: GPIO_APP_COUNTER1 = 0 0x10008: GPIO_APP_COUNTER2 = 0 0x10009: posedge of xc_trigger[0] 0x1000a: posedge of xc_trigger[1] 0x1000b: negedge of xc_trigger[0] 0x1000c: negedge of xc_trigger[1] 0x1000d: posedge of xc_sample[0] 0x1000e: posedge of xc_sample[1] 0x1

[16..0] Trigger condition for measurement

Definition at line 17578 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::tt_add |

[7..0] Tracking time addon

Definition at line 17443 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::val |

[14..0] result of measurement

Definition at line 17743 of file netx90_app.h.

| __IM uint32_t madc_seq0_Type::valid |

[31..31] result in register is finally calculated (val shows intermediate values in case of oversample>0)

Definition at line 17747 of file netx90_app.h.

| __IOM uint32_t madc_seq0_Type::vref_vdd3 |

[17..17] Reference Select of ADC: 0: use reference from pin VREF_ADC (internally driven C or external reference, s. madc_adc01_static_cfg-vref_buffer_enable) 1: use reference from pin VDD3 (Analog core supply)

Definition at line 17413 of file netx90_app.h.