|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

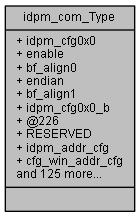

idpm_com (idpm_com) More...

#include <netx90_app.h>

idpm_com (idpm_com)

Definition at line 1409 of file netx90_app.h.

| union { ... } |

< (@ 0xFF001B00) idpm_com Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t idpm_com_Type::base |

[14..6] DPM Access Tunnel (DATunnel) Base Address divided by 64 on external visible address space. Note: Default setting for tunnel base is starting on external address 0x100.

[31..6] Internal netX Tunnel Target Base Address (ITBAddr) divided by 64. View description of dpm_tunnel_cfg register.

Definition at line 1493 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::bf_align0 |

[3..1] bitField alignment value for aeabi compatibility

[3..0] bitField alignment value for aeabi compatibility

[5..4] bitField alignment value for aeabi compatibility

[6..0] bitField alignment value for aeabi compatibility

[1..0] bitField alignment value for aeabi compatibility

[1..1] bitField alignment value for aeabi compatibility

[7..1] bitField alignment value for aeabi compatibility

[31..16] bitField alignment value for aeabi compatibility

[31..8] bitField alignment value for aeabi compatibility

[24..24] bitField alignment value for aeabi compatibility

[24..16] bitField alignment value for aeabi compatibility

Definition at line 1420 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::bf_align0 |

[31..1] bitField alignment value for aeabi compatibility

[1..1] bitField alignment value for aeabi compatibility

Definition at line 1461 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::bf_align1 |

[31..6] bitField alignment value for aeabi compatibility

[30..15] bitField alignment value for aeabi compatibility

[31..16] bitField alignment value for aeabi compatibility

[4..4] bitField alignment value for aeabi compatibility

[6..4] bitField alignment value for aeabi compatibility

[31..3] bitField alignment value for aeabi compatibility

[31..9] bitField alignment value for aeabi compatibility

[27..27] bitField alignment value for aeabi compatibility

Definition at line 1427 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::bf_align1 |

[31..3] bitField alignment value for aeabi compatibility

Definition at line 1716 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::bf_align2 |

[6..6] bitField alignment value for aeabi compatibility

[31..15] bitField alignment value for aeabi compatibility

Definition at line 1590 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::bf_align3 |

[31..15] bitField alignment value for aeabi compatibility

Definition at line 1601 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::cfg_win_addr_cfg |

[5..4] Location of the DPM Configuration Window (Window 0). Supported settings are: 00: Low Configuration Window: The Configuration Window is located in the first 256 bytes of external DPM address range (0x0 to 0xff). It is located before the first enabled Data Window (1 to 4). 01: High Configuration Window: The Configuration Window is located in the last 256 bytes of external DPM address range. Example: 'addr_range' is 8kB: Configuration Window is located in 0x1F00..0x1FFF. 10: reserved. 11: Configuration Window

Definition at line 1437 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::dpm_sw |

[0..0] raw software IRQ for IRQ targets interrupt

[0..0] masked software IRQ for IRQ targets interrupt state for IDPM host interrupt

Definition at line 1713 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::dpm_sw |

[0..0] set software IRQ for IRQ targets interrupt mask for IDPM host interrupt

[0..0] reset software IRQ for IRQ targets interrupt mask for IDPM host interrupt

Definition at line 1735 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::enable |

[0..0] Global IDPM enable bit. The IDPM module must be enabled by the INTLOGIC area before the host area (i.e. DPM mirrors of INTRAMHS) can be used. While disabled all host access (access to DPM mirrors of INTRAMHS) will be ignored. Read will return 0x0bad0bad.

[2..2] Enable/disable Access Tunnel function.

Definition at line 1415 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::endian |

[5..4] Endianess of 32 bit (DWord) address alignment (B0: least significant byte, B3: most significant byte): { | | | | | coding Address A+3 A+2 A+1 A+0 00 little endian B3 B2 B1 B0 01 16 bit big endian B2 B3 B0 B1 10 32 bit big endian B0 B1 B2 B3 11 reserved } Little endian is used netX inside. If big endian host device is used, set to this 01

Definition at line 1421 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::firmware |

[2..2] raw combined handshake-cell and SYS_STA firmware interrupt

[2..2] masked combined handshake-cell and SYS_STA firmware interrupt state for IDPM host interrupt

Definition at line 1715 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::firmware |

[2..2] set combined handshake-cell and SYS_STA firmware interrupt mask for IDPM host interrupt

[2..2] reset combined handshake-cell and SYS_STA firmware interrupt mask for IDPM host interrupt

Definition at line 1738 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HOST_STATE |

[7..4] Bit field for Hilscher firmware. Note: This bit field can NOT be read from 'netx_status'-register inside ASIC_CTRL address area.

Definition at line 1839 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT0 |

[0..0] Handshake Event 0 IRQ status flag.

[0..0] Handshake Event 0 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1882 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT1 |

[1..1] Handshake Event 1 IRQ status flag.

[1..1] Handshake Event 1 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1883 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT10 |

[10..10] Handshake Event 10 IRQ status flag.

[10..10] Handshake Event 10 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1892 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT11 |

[11..11] Handshake Event 11 IRQ status flag.

[11..11] Handshake Event 11 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1893 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT12 |

[12..12] Handshake Event 12 IRQ status flag.

[12..12] Handshake Event 12 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1894 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT13 |

[13..13] Handshake Event 13 IRQ status flag.

[13..13] Handshake Event 13 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1895 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT14 |

[14..14] Handshake Event 14 IRQ status flag.

[14..14] Handshake Event 14 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1896 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT15 |

[15..15] Handshake Event 15 IRQ status flag.

[15..15] Handshake Event 15 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1897 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT2 |

[2..2] Handshake Event 2 IRQ status flag.

[2..2] Handshake Event 2 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1884 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT3 |

[3..3] Handshake Event 3 IRQ status flag.

[3..3] Handshake Event 3 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1885 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT4 |

[4..4] Handshake Event 4 IRQ status flag.

[4..4] Handshake Event 4 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1886 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT5 |

[5..5] Handshake Event 5 IRQ status flag.

[5..5] Handshake Event 5 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1887 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT6 |

[6..6] Handshake Event 6 IRQ status flag.

[6..6] Handshake Event 6 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1888 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT7 |

[7..7] Handshake Event 7 IRQ status flag.

[7..7] Handshake Event 7 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1889 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT8 |

[8..8] Handshake Event 8 IRQ status flag.

[8..8] Handshake Event 8 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1890 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::HS_EVENT9 |

[9..9] Handshake Event 9 IRQ status flag.

[9..9] Handshake Event 9 IRQ Enable (also netX-controllable by HANDSHAKE_CTRL, netX50 comp.).

Definition at line 1891 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::idpm_addr_cfg |

(@ 0x00000010) DPM External Address Configuration Register.

Definition at line 1433 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_addr_cfg_b |

| __IOM uint32_t idpm_com_Type::idpm_cfg0x0 |

(@ 0x00000000) DPM IO Control Register 0.

Definition at line 1412 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_cfg0x0_b |

| __IOM uint32_t idpm_com_Type::idpm_firmware_irq_mask |

(@ 0x000000F0) DPM Handshake Interrupt Enable Register. Only netx50 compatible 'dpm_firmware_irq' registers are related to settings of this register. Note: This register is compatible to netx50 DPM_HOST_INT_EN0 register, however some unused IRQs have been removed. Note: HS_EVENT-bits are not read-only. This is netX50 compliant. Recent netX50 Documentation marks HS_EVENT-bits as read-only. This is an dokumentation error. For netX50 compatibility, these bits can also be controlled from netX-side i

Definition at line 1930 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_firmware_irq_mask_b |

| __IOM uint32_t idpm_com_Type::idpm_firmware_irq_raw |

(@ 0x000000E0) 1st netx50 compatible DPM Interrupt Status Register (related to 'dpm_firmware_irq_mask'-register). Writing a '1' to an IRQ flag will clear the Interrupt. This is always done even if related bit inside 'dpm_firmware_irq_mask'-register is not set (this is compatible to netx50). Important: There are two completely independent sets of IRQ registers: IRQ register-set 1: 'dpm_irq_raw' (and related registers e.g. 'dpm_irq_irq_*' registers). IRQ register-set 2: 'dpm_firmware_irq_* register

Definition at line 1869 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_firmware_irq_raw_b |

| __IOM uint32_t idpm_com_Type::idpm_irq_host_mask_reset |

(@ 0x00000088) DPM Interrupt Mask Reset Register for IDPM host interrupt. Write access with '1' resets related interrupt mask bits (disables interrupt request for corresponding interrupt source). Write access with '0' does not influence related interrupt mask bit. Read access shows actual interrupt mask. If a mask bit is set, the related interrupt will activate the IRQ for IDPM host interrupt. Interrupts must be reset in interrupt generating module. Interrupts cannot be cleared here. To release IRQ for IDP

Definition at line 1745 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_irq_host_mask_reset_b |

| __IOM uint32_t idpm_com_Type::idpm_irq_host_mask_set |

(@ 0x00000084) DPM Interrupt Mask Register for IDPM host interrupt. Write access with '1' sets related interrupt mask bits (enables interrupt request for corresponding interrupt source). Write access with '0' does not influence related interrupt mask bit. Read access shows actual interrupt mask. If a mask bit is set, the related interrupt will activate the IRQ for IDPM host interrupt. Interrupts must be reset in interrupt generating module. Interrupts cannot be cleared here. To release IRQ for IDPM host in

Definition at line 1721 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_irq_host_mask_set_b |

| __IM uint32_t idpm_com_Type::idpm_irq_host_masked |

(@ 0x0000008C) DPM Masked Interrupt Status Register for IDPM host interrupt. A bit is set, when the related mask bit is set in 'dpm_irq_host_mask'-register and the related interrupt is asserted. IRQ for IDPM host interrupt is asserted if at least one bit is set here. Interrupts must be reset in interrupt generating module. Interrupts cannot be cleared here. To release IRQ for IDPM host interrupt without clearing interrupt in module, reset related mask bit to 0. Note: For further information view descri

Definition at line 1769 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_irq_host_masked_b |

| __IM uint32_t idpm_com_Type::idpm_irq_raw |

(@ 0x00000080) DPM Raw (before masking) IRQ Status Register. If a bit is set, the related interrupt is asserted. Interrupts must be reset in interrupt generating module. Interrupts cannot be cleared here. Important: There are two completely independent sets of IRQ registers: IRQ register-set 1: 'dpm_irq_raw' (and related registers e.g. 'dpm_irq_irq_*' registers). IRQ register-set 2: 'dpm_firmware_irq_* registers' (netx50 compatible register set: DPM_HOST_INT_EN0,2 DPM_HOST_INT_STA0,2). Programmin

Definition at line 1700 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_irq_raw_b |

| __IOM uint32_t idpm_com_Type::idpm_itbaddr |

(@ 0x0000003C) DPM Access Tunnel (DATunnel) netX Internal Target Base Address (ITBAddr) Configuration Register. For DPM Access Tunnel (DATunnel) function view description of dpm_tunnel_cfg register. This register contains ITBAddr value that can also be changed by host on last offset 0x3c (last DWord) of external DATunnel area (defined by bit field 'base' in 'dpm_tunnel_cfg' register). However this register can also be write-protected from host if bit 'wp_itbaddr' in 'dpm_tunnel_cfg' register is set. Write

Definition at line 1510 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_itbaddr_b |

| __IM uint32_t idpm_com_Type::idpm_netx_version |

(@ 0x000000FC) DPM netX Version Register. This register is mirrored form asic_ctrl register area and can be set during netX booting phase by netX firmware. This register is not valid if unlocked bit is not set in dpm_status register.

Definition at line 1999 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_netx_version_b |

| __IOM uint32_t idpm_com_Type::idpm_reset_request |

(@ 0x000000DC) DPM Reset Request Register. Note: This register is compatible to netx50 DPM_HOST_RESET_REQ register

Definition at line 1850 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_reset_request_b |

| __IM uint32_t idpm_com_Type::idpm_status |

(@ 0x0000001C) DPM Status Register.

Definition at line 1452 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_status_b |

| __IOM uint32_t idpm_com_Type::idpm_sw_irq |

(@ 0x000000C0) DPM Register for Software Interrupt Generation to Host and netX Interrupt Targets. Host and netX masters can generate an interrupt to netX interrupt targets (e.g. ARM-VIC) by this register. To propagate interrupt states from this register to the interrupt target the 'idpm_sw' IRQ must be enabled inside the appropriate interrupt controller (e.g. the ARM-VIC). Note: There is a set and a reset bit for the sw-IRQ to avoid read-modify-write sequences. When both (set and reset) bits are set

Definition at line 1794 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_sw_irq_b |

| __IOM uint32_t idpm_com_Type::idpm_sys_sta |

(@ 0x000000D8) DPM System Status Information Register. This register can be used for firmware status information. Note: This register is NOT fully compatible to netx50 DPM_HOST_SYS_STAT register: Only the HOST_STATE-bits of DPM0 can be read from the 'netx_status'-register inside ASIC_CTRL address area. The HOST_STATE-bits of DPM1 and IDPM can not be read from the 'netx_status'-register inside ASIC_CTRL address area.

Definition at line 1818 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_sys_sta_b |

| __IOM uint32_t idpm_com_Type::idpm_tunnel_cfg |

(@ 0x00000038) description too long, please enter short description.

Definition at line 1467 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_tunnel_cfg_b |

| __IOM uint32_t idpm_com_Type::idpm_win1_end |

(@ 0x00000040) DPM Window 1 End Address Configuration Register. Smallest DPM window configuration unit is 128 bytes (i.e. lowest 7 bits of address configuration are always 0). At address 0x0 DPM configuration window is mapped after reset (length: 256 bytes, containing all DPM addresses defined here). Each window starts at window end address of the preceding window. Hence external window 1 start address is 0x100, window 2 starts at value programmed in this register and so on. Note: This register can be w

Definition at line 1539 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_win1_end_b |

| __IOM uint32_t idpm_com_Type::idpm_win1_map |

(@ 0x00000044) DPM Window 1 Address Map Configuration Register. Smallest DPM window configuration unit is 128 bytes (i.e. lowest 7 bits of address configuration are always 0). For further information view description of 'dpm_win1_end' register.

Definition at line 1562 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_win1_map_b |

| __IOM uint32_t idpm_com_Type::idpm_win2_end |

(@ 0x00000048) DPM Window 2 End Address Configuration Register. For detailed information refer to 'idpm_win1_end' register description. Note: This register can be write-protected by the 'wp_cfg_win'-bit of the 'idpm_win1_map' register.

Definition at line 1606 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_win2_end_b |

| __IOM uint32_t idpm_com_Type::idpm_win2_map |

(@ 0x0000004C) DPM Window 2 Address Map Configuration Register. For detailed information refer to 'dpm_win1_map' register description. Note: This register can be write-protected by the 'wp_cfg_win'-bit of the 'idpm_win1_map' register.

Definition at line 1621 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_win2_map_b |

| __IOM uint32_t idpm_com_Type::idpm_win3_end |

(@ 0x00000050) DPM Window 3 End Address Configuration Register. For detailed information refer to 'idpm_win1_end' register description. Note: This register can be write-protected by the 'wp_cfg_win'-bit of the 'idpm_win1_map' register.

Definition at line 1637 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_win3_end_b |

| __IOM uint32_t idpm_com_Type::idpm_win3_map |

(@ 0x00000054) DPM Window 3 Address Map Configuration Register. For detailed information refer to 'dpm_win1_map' register description. Note: This register can be write-protected by the 'wp_cfg_win'-bit of the 'idpm_win1_map' register.

Definition at line 1652 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_win3_map_b |

| __IOM uint32_t idpm_com_Type::idpm_win4_end |

(@ 0x00000058) DPM Window 4 End Address Configuration Register. For detailed information refer to 'idpm_win1_end' register description. Note: This register can be write-protected by the 'wp_cfg_win'-bit of the 'idpm_win1_map' register.

Definition at line 1668 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_win4_end_b |

| __IOM uint32_t idpm_com_Type::idpm_win4_map |

(@ 0x0000005C) DPM Window 4 Address Map Configuration Register. For detailed information refer to 'dpm_win1_map' register description. Note: This register can be write-protected by the 'wp_cfg_win'-bit of the 'idpm_win1_map' register.

Definition at line 1683 of file netx90_app.h.

| struct { ... } idpm_com_Type::idpm_win4_map_b |

| __IOM uint32_t idpm_com_Type::INT_EN |

[31..31] Interrupt Enable for IRQs handled in this register. Only if this bit is set, global firmware IRQ will be asserted to host CPU, ARM or xPIC by dpm_irq_* registers. 0: No Interrupts to host, ARM or xPIC are generated by IRQ sources handled in this register. 1: Enabled IRQ sources handled in this register generate a host, ARM or xPIC IRQ if asserted. Note: Enable bits for single IRQ events are not affected if this bit is set or reset.

Definition at line 1986 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::INT_REQ |

[31..31] Interrupt Request for IRQs handled in this register. 0: No Interrupts to host requested by IRQ sources handled in this register. 1: IRQ sources handled in this register request a host IRQ. Note: This bit is masked by INT_EN-bit in dpm_firmware_irq_mask register. For propagation of INT_REQ to host, ARM or xPIC, INT_EN-bit must be set and firmware IRQ must be activated in related dpm_irq_* register.

Definition at line 1918 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::IRQ_VECTOR |

[23..16] Interrupt Vector according to status flags generated by enabled IRQ sources. { | Code IRQ status 0x00 No IRQ. -— ----— 0x10 Handshake Cell 0 IRQ. 0x11 Handshake Cell 1 IRQ. 0x12 Handshake Cell 2 IRQ. 0x13 Handshake Cell 3 IRQ. 0x14 Handshake Cell 4 IRQ. 0x15 Handshake Cell 5 IRQ. 0x16 Handshake Cell 6 IRQ. 0x17 Handshake Cell 7 IRQ. 0x18 Handshake Cell 8 IRQ. 0x19 Handshake Cell 9 IRQ. 0x1a Handshake Cell 10 IRQ. 0x1b Handshake Cell 11 IRQ. 0x1c Handshake Cell 12 IRQ

Definition at line 1898 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::map |

[5..2] Mapping part of ITBAddr. View description of dpm_tunnel_cfg register.

Definition at line 1531 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::NETX_STA_CODE_ro |

[15..8] Bit field for Hilscher firmware compatibility (read only). Note: This bit field can be changed by 'netx_status'-register inside ASIC_CTRL address area.

Definition at line 1842 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::NETX_STATE_ro |

[3..2] Bit field for Hilscher firmware compatibility. Note: This bit field can be changed by 'netx_status'-register inside ASIC_CTRL address area.

Definition at line 1836 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::netx_version |

[31..0] netX version from version register.

Definition at line 2006 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::RDY_ro |

[0..0] Output state of netX RDY LED IO. Note: This bit field can be changed by 'rdy_run_cfg'-register inside ASIC_CTRL address area.

Definition at line 1830 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::res_MEM_LCK_ro |

[30..30] reserved for Memory Lock IRQ flag (not available in this netX version).

[30..30] reserved for Memory Lock IRQ (not available in this netX version).

Definition at line 1916 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::res_RDY_TIMEOUT_ro |

[28..28] reserved, DPM_RDY timeout error does not exist for IDPM.

Definition at line 1912 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::res_TMR_ro |

[25..25] reserved for Timer IRQ flag (not available in this netX version).

[25..25] reserved for Timer IRQ (not available in this netX version).

Definition at line 1908 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::res_WDG_NETX_ro |

[29..29] reserved for netX supervision Watchdog Timeout IRQ flag (not available in this netX version).

[29..29] reserved for netX supervision Watchdog Timeout IRQ (not available in this netX version).

Definition at line 1914 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::RESERVED[3] |

Definition at line 1430 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::RESERVED1[2] |

Definition at line 1449 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::RESERVED2[6] |

Definition at line 1464 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::RESERVED3[8] |

Definition at line 1697 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::RESERVED4[12] |

Definition at line 1791 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::RESERVED5[5] |

Definition at line 1815 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::RESERVED6[3] |

Definition at line 1927 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::RESERVED7[2] |

Definition at line 1996 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::reset_host |

[8..8] Reset 'dpm_sw' IRQ for host (always 0 when read)

Definition at line 1811 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::reset_key |

[7..0] Reset key sequence register. A netx hardware reset is generated if the following sequence is written to this register: 1st access: write 0x00 2nd access: write 0x01 3rd access: write 0x03 4th access: write 0x07 5th access: write 0x0f 6th access: write 0x1f 7th access: write 0x3f 8th access: write 0x7f To issue a reset the sequence must not be interrupted by a write access to another register of this DPM module register area. Writing 0x00 will always restart the sequence. Reading thi

Definition at line 1855 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::RUN_ro |

[1..1] Output state of netX RUN LED IO. Note: This bit field can be changed by 'rdy_run_cfg'-register inside ASIC_CTRL address area.

Definition at line 1833 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::set_host |

[0..0] Set 'dpm_sw' IRQ for host (current 'dpm_sw' status for host when read)

Definition at line 1808 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::SYS_STA |

[26..26] System Status Change IRQ flag.

[26..26] System Status Change IRQ Enable.

Definition at line 1910 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::tunnel_all |

[3..3] Enable/disable the ITBAddr configuration register at tunnel offset 0x3C. 0: Only 15 DWords are tunneled to the internal tunnel target. The idpm_itbaddr is available at offset 0x3C. One DWord of the tunnel target area is hidden by idpm_itbaddr. 1: All 16 DWords are tunneled to the internal tunnel target. The idpm_itbaddr is not available at offset 0x3C. All 64 tunnel target bytes can be reached (no hidden register). Note: Target mapping (base and map) will not be affected by this bit. Using a 'map' value no

Definition at line 1483 of file netx90_app.h.

| __IM uint32_t idpm_com_Type::unlocked |

[0..0] DPM is locked during netX power up and boot phase. DPM access to other addresses than DPM configuration window 0 cannot be done before this bit is set to 1. Write access to data windows (netX AHB area) will be ignored and read access will deliver invalid data while locked. Poll for 1 after power-up or reset.

Definition at line 1455 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::win_end |

[15..7] Window 1 End Address divided by 128. Last external address is win_end*128-1. Setting win_end to 0 will disable this window.

[15..7] Window 2 End Address divided by 128. Last external address is win_end*128-1.

[15..7] Window 3 End Address divided by 128. Last external address is win_end*128-1.

[15..7] Window 4 End Address divided by 128. Last external address is win_end*128-1.

Definition at line 1554 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::win_map |

[14..7] Window 1 Address Mapping. Internal access address HADDR to netX logic is combined by DPM interface by: HADDR[31:16]: unchanged, as it comes form accessing master HADDR[15:0]: mapped DPM address. This part of address is defined by programmed win_map value for each window. The value to be programmed is address bits 15 to 0 of netX internal window start address minus start address of the external window (i.e. end address of preceding window) . Example: Window n starts at 0x400 of external DPM address range (

[14..7] Window address mapping.

[14..7] Window map address.

Definition at line 1591 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::win_map_alt |

[3..2] Window 1 Alternative Address Mapping Configuration. Alternative Address Mapping can be generated by Triple Buffer Managers inside HANDSHAKE_CTRL unit. Coding: 00 : Alternative Address Mapping disabled. 01 : Alternative Address Mapping enabled: Use Triple Buffer Manager 0 from HANDSHAKE_CTRL unit. 10 : Alternative Address Mapping enabled: Use Triple Buffer Manager 1 from HANDSHAKE_CTRL unit. 11 : reserved If Alternative Address Mapping is enabled, mapping value is taken according to buffer status of related

[3..2] Window Alternative Address Mapping Configuration.

Definition at line 1571 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::wp_cfg_win |

[31..31] Write-protect tunnel configuration inside the configuration window 0. 0: The two tunnel configuration registers ('idpm_tunnel_cfg' and 'idpm_itbaddr') can be programmed via configuration window 0 and the INTLOGIC_SYS-IDPM address area. 1: The tunnel configuration registers ('idpm_tunnel_cfg' and 'idpm_itbaddr') cannot be programmed by the host via configuration window 0 (they are read-only for the host there). They can only be programmed via the INTLOGIC_SYS-IDPM address area. Note: Set this bit to protect

[5..5] Write-protect window configuration inside the configuration window 0. 0: All 8 window configuration registers ('dpm_winX_and' and 'dpm_winX_map') can be programmed via configuration window 0 and the INTLOGIC-DPM address area. 1: All 8 window configuration registers ('dpm_winX_and' and 'dpm_winX_map') cannot be programmed by the host via configuration window 0 (they are read-only for the host there). They can only be programmed via the INTLOGIC-DPM address area. Note: Set this bit to protect the NETX from r

Definition at line 1497 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::wp_data |

[0..0] Access Tunnel function is write-protected for data access (DWords 0 to 14 (15 for 'tunnel_all') of DATunnel). 0: Write access is forwarded through the tunnel. 1: Write access to DWords 0 to 14 (15 for 'tunnel_all') of DATunnel will be ignored. Data write protection for host is enabled by default and can be disabled by clearing this bit.

Definition at line 1470 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::wp_data_ro |

[0..0] Access Tunnel function is write-protected from data access (DWords 0 to 14 of DATunnel). This is a read-only bit here. Its setting can be changed in 'dpm_tunnel_cfg' register. View description of dpm_tunnel_cfg register.

Definition at line 1524 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::wp_itbaddr |

[1..1] ITBAddr is write-protected from host. 0: The ITBAddr is mirrored to offset 0x3C of the tunnel and can also be programmed there. 1: ITBAddr (Internal netX 32 bit Tunnel Target Base Address) is read-only for tunnel offset 0x3C. It can only be changed via configuration window 0 idpm_itbaddr address or the INTLOGIC IDPM area.

Definition at line 1476 of file netx90_app.h.

| __IOM uint32_t idpm_com_Type::wp_itbaddr_ro |

[1..1] ITBAddr is write-protected from host. This is a read-only bit here. Its setting can be changed in 'dpm_tunnel_cfg' register. View description of dpm_tunnel_cfg register.

Definition at line 1528 of file netx90_app.h.