|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

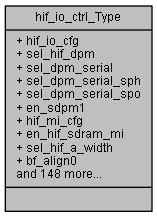

hif_io_ctrl (hif_io_ctrl) More...

#include <netx90_app.h>

Data Fields | |

| union { | |

| __IOM uint32_t hif_io_cfg | |

| struct { | |

| __IOM uint32_t sel_hif_dpm: 1 | |

| __IOM uint32_t sel_dpm_serial: 1 | |

| __IOM uint32_t sel_dpm_serial_sph: 1 | |

| __IOM uint32_t sel_dpm_serial_spo: 1 | |

| __IOM uint32_t en_sdpm1: 1 | |

| __IOM uint32_t hif_mi_cfg: 2 | |

| __IOM uint32_t en_hif_sdram_mi: 1 | |

| __IOM uint32_t sel_hif_a_width: 4 | |

| __IOM uint32_t bf_align0: 12 | |

| __IOM uint32_t en_hif_rdy_pio_mi: 1 | |

| __IOM uint32_t en_hif_wdg_sys_hif_d19: 1 | |

| __IOM uint32_t bf_align1: 6 | |

| } hif_io_cfg_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_cfg | |

| struct { | |

| __IOM uint32_t in_ctrl: 2 | |

| __IOM uint32_t bf_align0: 1 | |

| __IOM uint32_t filter_en_in: 1 | |

| __IOM uint32_t bf_align1: 12 | |

| __IOM uint32_t irq_hif_d12_cfg: 2 | |

| __IOM uint32_t irq_hif_a16_cfg: 2 | |

| __IOM uint32_t irq_hif_a17_cfg: 2 | |

| __IOM uint32_t bf_align2: 4 | |

| __IOM uint32_t irq_hif_dirq_cfg: 2 | |

| __IOM uint32_t bf_align3: 3 | |

| __IOM uint32_t filter_irqs: 1 | |

| } hif_pio_cfg_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_out0 | |

| struct { | |

| __IOM uint32_t hif_d0: 1 | |

| __IOM uint32_t hif_d1: 1 | |

| __IOM uint32_t hif_d2: 1 | |

| __IOM uint32_t hif_d3: 1 | |

| __IOM uint32_t hif_d4: 1 | |

| __IOM uint32_t hif_d5: 1 | |

| __IOM uint32_t hif_d6: 1 | |

| __IOM uint32_t hif_d7: 1 | |

| __IOM uint32_t hif_d8: 1 | |

| __IOM uint32_t hif_d9: 1 | |

| __IOM uint32_t hif_d10: 1 | |

| __IOM uint32_t hif_d11: 1 | |

| __IOM uint32_t hif_d12: 1 | |

| __IOM uint32_t hif_d13: 1 | |

| __IOM uint32_t hif_d14: 1 | |

| __IOM uint32_t hif_d15: 1 | |

| __IOM uint32_t bf_align0: 16 | |

| } hif_pio_out0_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_out1 | |

| struct { | |

| __IOM uint32_t hif_a0: 1 | |

| __IOM uint32_t hif_a1: 1 | |

| __IOM uint32_t hif_a2: 1 | |

| __IOM uint32_t hif_a3: 1 | |

| __IOM uint32_t hif_a4: 1 | |

| __IOM uint32_t hif_a5: 1 | |

| __IOM uint32_t hif_a6: 1 | |

| __IOM uint32_t hif_a7: 1 | |

| __IOM uint32_t hif_a8: 1 | |

| __IOM uint32_t hif_a9: 1 | |

| __IOM uint32_t hif_a10: 1 | |

| __IOM uint32_t hif_a11: 1 | |

| __IOM uint32_t hif_a12: 1 | |

| __IOM uint32_t hif_a13: 1 | |

| __IOM uint32_t hif_a14: 1 | |

| __IOM uint32_t hif_a15: 1 | |

| __IOM uint32_t hif_a16: 1 | |

| __IOM uint32_t hif_a17: 1 | |

| __IOM uint32_t bf_align0: 7 | |

| __IOM uint32_t hif_bhen: 1 | |

| __IOM uint32_t hif_rdn: 1 | |

| __IOM uint32_t hif_wrn: 1 | |

| __IOM uint32_t hif_csn: 1 | |

| __IOM uint32_t hif_rdy: 1 | |

| __IOM uint32_t hif_dirq: 1 | |

| __IOM uint32_t hif_sdclk: 1 | |

| } hif_pio_out1_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_oe0 | |

| struct { | |

| __IOM uint32_t hif_d0: 1 | |

| __IOM uint32_t hif_d1: 1 | |

| __IOM uint32_t hif_d2: 1 | |

| __IOM uint32_t hif_d3: 1 | |

| __IOM uint32_t hif_d4: 1 | |

| __IOM uint32_t hif_d5: 1 | |

| __IOM uint32_t hif_d6: 1 | |

| __IOM uint32_t hif_d7: 1 | |

| __IOM uint32_t hif_d8: 1 | |

| __IOM uint32_t hif_d9: 1 | |

| __IOM uint32_t hif_d10: 1 | |

| __IOM uint32_t hif_d11: 1 | |

| __IOM uint32_t hif_d12: 1 | |

| __IOM uint32_t hif_d13: 1 | |

| __IOM uint32_t hif_d14: 1 | |

| __IOM uint32_t hif_d15: 1 | |

| __IOM uint32_t bf_align0: 16 | |

| } hif_pio_oe0_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_oe1 | |

| struct { | |

| __IOM uint32_t hif_a0: 1 | |

| __IOM uint32_t hif_a1: 1 | |

| __IOM uint32_t hif_a2: 1 | |

| __IOM uint32_t hif_a3: 1 | |

| __IOM uint32_t hif_a4: 1 | |

| __IOM uint32_t hif_a5: 1 | |

| __IOM uint32_t hif_a6: 1 | |

| __IOM uint32_t hif_a7: 1 | |

| __IOM uint32_t hif_a8: 1 | |

| __IOM uint32_t hif_a9: 1 | |

| __IOM uint32_t hif_a10: 1 | |

| __IOM uint32_t hif_a11: 1 | |

| __IOM uint32_t hif_a12: 1 | |

| __IOM uint32_t hif_a13: 1 | |

| __IOM uint32_t hif_a14: 1 | |

| __IOM uint32_t hif_a15: 1 | |

| __IOM uint32_t hif_a16: 1 | |

| __IOM uint32_t hif_a17: 1 | |

| __IOM uint32_t bf_align0: 7 | |

| __IOM uint32_t hif_bhen: 1 | |

| __IOM uint32_t hif_rdn: 1 | |

| __IOM uint32_t hif_wrn: 1 | |

| __IOM uint32_t hif_csn: 1 | |

| __IOM uint32_t hif_rdy: 1 | |

| __IOM uint32_t hif_dirq: 1 | |

| __IOM uint32_t hif_sdclk: 1 | |

| } hif_pio_oe1_b | |

| }; | |

| union { | |

| __IM uint32_t hif_pio_in0 | |

| struct { | |

| __IM uint32_t hif_d0: 1 | |

| __IM uint32_t hif_d1: 1 | |

| __IM uint32_t hif_d2: 1 | |

| __IM uint32_t hif_d3: 1 | |

| __IM uint32_t hif_d4: 1 | |

| __IM uint32_t hif_d5: 1 | |

| __IM uint32_t hif_d6: 1 | |

| __IM uint32_t hif_d7: 1 | |

| __IM uint32_t hif_d8: 1 | |

| __IM uint32_t hif_d9: 1 | |

| __IM uint32_t hif_d10: 1 | |

| __IM uint32_t hif_d11: 1 | |

| __IM uint32_t hif_d12: 1 | |

| __IM uint32_t hif_d13: 1 | |

| __IM uint32_t hif_d14: 1 | |

| __IM uint32_t hif_d15: 1 | |

| __IM uint32_t bf_align0: 16 | |

| } hif_pio_in0_b | |

| }; | |

| union { | |

| __IM uint32_t hif_pio_in1 | |

| struct { | |

| __IM uint32_t hif_a0: 1 | |

| __IM uint32_t hif_a1: 1 | |

| __IM uint32_t hif_a2: 1 | |

| __IM uint32_t hif_a3: 1 | |

| __IM uint32_t hif_a4: 1 | |

| __IM uint32_t hif_a5: 1 | |

| __IM uint32_t hif_a6: 1 | |

| __IM uint32_t hif_a7: 1 | |

| __IM uint32_t hif_a8: 1 | |

| __IM uint32_t hif_a9: 1 | |

| __IM uint32_t hif_a10: 1 | |

| __IM uint32_t hif_a11: 1 | |

| __IM uint32_t hif_a12: 1 | |

| __IM uint32_t hif_a13: 1 | |

| __IM uint32_t hif_a14: 1 | |

| __IM uint32_t hif_a15: 1 | |

| __IM uint32_t hif_a16: 1 | |

| __IM uint32_t hif_a17: 1 | |

| __IM uint32_t bf_align0: 7 | |

| __IM uint32_t hif_bhen: 1 | |

| __IM uint32_t hif_rdn: 1 | |

| __IM uint32_t hif_wrn: 1 | |

| __IM uint32_t hif_csn: 1 | |

| __IM uint32_t hif_rdy: 1 | |

| __IM uint32_t hif_dirq: 1 | |

| __IM uint32_t hif_sdclk: 1 | |

| } hif_pio_in1_b | |

| }; | |

| __IM uint32_t | RESERVED |

| union { | |

| __IOM uint32_t hif_pio_irq_raw | |

| struct { | |

| __IOM uint32_t irq_hif_d12: 1 | |

| __IOM uint32_t irq_hif_a16: 1 | |

| __IOM uint32_t irq_hif_a17: 1 | |

| __IOM uint32_t irq_hif_dirq: 1 | |

| __IOM uint32_t bf_align0: 28 | |

| } hif_pio_irq_raw_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_irq_arm_mask_set | |

| struct { | |

| __IOM uint32_t irq_hif_d12: 1 | |

| __IOM uint32_t irq_hif_a16: 1 | |

| __IOM uint32_t irq_hif_a17: 1 | |

| __IOM uint32_t irq_hif_dirq: 1 | |

| __IOM uint32_t bf_align0: 28 | |

| } hif_pio_irq_arm_mask_set_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_irq_arm_mask_reset | |

| struct { | |

| __IOM uint32_t irq_hif_d12: 1 | |

| __IOM uint32_t irq_hif_a16: 1 | |

| __IOM uint32_t irq_hif_a17: 1 | |

| __IOM uint32_t irq_hif_dirq: 1 | |

| __IOM uint32_t bf_align0: 28 | |

| } hif_pio_irq_arm_mask_reset_b | |

| }; | |

| union { | |

| __IM uint32_t hif_pio_irq_arm_masked | |

| struct { | |

| __IM uint32_t irq_hif_d12: 1 | |

| __IM uint32_t irq_hif_a16: 1 | |

| __IM uint32_t irq_hif_a17: 1 | |

| __IM uint32_t irq_hif_dirq: 1 | |

| __IM uint32_t bf_align0: 28 | |

| } hif_pio_irq_arm_masked_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_irq_xpic_mask_set | |

| struct { | |

| __IOM uint32_t irq_hif_d12: 1 | |

| __IOM uint32_t irq_hif_a16: 1 | |

| __IOM uint32_t irq_hif_a17: 1 | |

| __IOM uint32_t irq_hif_dirq: 1 | |

| __IOM uint32_t bf_align0: 28 | |

| } hif_pio_irq_xpic_mask_set_b | |

| }; | |

| union { | |

| __IOM uint32_t hif_pio_irq_xpic_mask_reset | |

| struct { | |

| __IOM uint32_t irq_hif_d12: 1 | |

| __IOM uint32_t irq_hif_a16: 1 | |

| __IOM uint32_t irq_hif_a17: 1 | |

| __IOM uint32_t irq_hif_dirq: 1 | |

| __IOM uint32_t bf_align0: 28 | |

| } hif_pio_irq_xpic_mask_reset_b | |

| }; | |

| union { | |

| __IM uint32_t hif_pio_irq_xpic_masked | |

| struct { | |

| __IM uint32_t irq_hif_d12: 1 | |

| __IM uint32_t irq_hif_a16: 1 | |

| __IM uint32_t irq_hif_a17: 1 | |

| __IM uint32_t irq_hif_dirq: 1 | |

| __IM uint32_t bf_align0: 28 | |

| } hif_pio_irq_xpic_masked_b | |

| }; | |

hif_io_ctrl (hif_io_ctrl)

Definition at line 14749 of file netx90_app.h.

| union { ... } |

< (@ 0xFF401480) hif_io_ctrl Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t hif_io_ctrl_Type::bf_align0 |

[23..12] bitField alignment value for aeabi compatibility

[2..2] bitField alignment value for aeabi compatibility

[31..16] bitField alignment value for aeabi compatibility

[24..18] bitField alignment value for aeabi compatibility

[31..4] bitField alignment value for aeabi compatibility

Definition at line 14818 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::bf_align0 |

[31..16] bitField alignment value for aeabi compatibility

[24..18] bitField alignment value for aeabi compatibility

[31..4] bitField alignment value for aeabi compatibility

Definition at line 15054 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::bf_align1 |

[31..26] bitField alignment value for aeabi compatibility

[15..4] bitField alignment value for aeabi compatibility

Definition at line 14833 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::bf_align2 |

[25..22] bitField alignment value for aeabi compatibility

Definition at line 14863 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::bf_align3 |

[30..28] bitField alignment value for aeabi compatibility

Definition at line 14873 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::en_hif_rdy_pio_mi |

[24..24] Enable HIF_RDY for PIO usage (or other netX MUX function) when the HIF is in memory-mode. Note: This bit must be disabled if HIF_RDY is used as EXT_BUS RDY (extension bus ready input). Note: This bit is ignored if HIF is DPM. Use DPM RDY configuration if HIF_RDY should be used as PIO together with DPM functionality.

Definition at line 14819 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::en_hif_sdram_mi |

[7..7] Enable HIF IOs for SDRAM Memory Interface configuration. HIF-SDRAM Chip-Select is generated on HIF_CSN when this bit is set. ExtBus Chip-Select area 0 is not available then. Ready-Signal for ExtBus is never available when SDRAM is enabled here. If enabled following IOs are used for SDRAM (netX90, partial shared with SRAM/FLASH ctrl signals): { | | netX90 IO Function Comment HIF_A0..12 SD_A0..12 Shared SDRAM/FLASH/SRAM address lines, small SDRAM devices do not nee

Definition at line 14800 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::en_hif_wdg_sys_hif_d19 |

[25..25] Obsolete for netX90, removed by regdef filter script. Enable 'wdg_active'/'WDGACT'-signal of netX system watchdog on HIF_D19. # default 0 When this bit is set HIF_D19 will be set to output mode and provide watchdog-active signal. However this will have no effect when HIF_D19 is used for another function. For parallel DPM with watchdog HIF_D19 must be set to PIO mode inside DPM module. Note: netX system watch can be programmed inside address area 'WATCHDOG'/'NETX_WDG_AREA'.

Definition at line 14825 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::en_sdpm1 |

[4..4] Enables the 2nd serial DPM for netX90. 0: 2nd serial DPM is disabled. 1: 2nd serial DPM is enabled. Note: It is possible to enable the 2nd serial DPM stand-alone or together with the normal DPM in serial mode (i.e. both bits 'sel_hif_dpm' and 'sel_dpm_serial' set). It is not possible to use the 2nd serial DPM together with the first DPM in parallel mode as they use the same IOs (the 2nd DPM does not provide the parallel mode). Note: The mode of the 2nd serial DPM is same as for the first DPM (programmed by

Definition at line 14789 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::filter_en_in |

[3..3] HIF PIO Input sampling enable (EN_IN) filter. 0 Spikes will not be suppressed for EN_IN. 1 Spikes up to 10ns will be suppressed by HIF PIO EN_IN sample stages. Note: Spike suppression can only done for EN_IN input. There is no spike suppression for data inputs of 'hif_pio_in0,1' registers.

Definition at line 14851 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::filter_irqs |

[31..31] Filtering of HIF PIO inputs for IRQ generation. By default filtering is applied on HIF PIO inputs before IRQ generation. 0 Spikes on PIOs will not be suppressed for HIF PIO IRQ generation. 1 Spikes up to 10ns on HIF PIOs will be suppressed by sample stages for HIF PIO IRQ generation. That causes 10ns additionally IRQ latency.

Definition at line 14874 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a0 |

[0..0] PIO output drive level of HIF_A0 signal.

[0..0] PIO output enable of HIF_A0 signal.

Definition at line 14927 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a0 |

[0..0] PIO input state of HIF_A0 signal.

Definition at line 15065 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a1 |

[1..1] PIO output drive level of HIF_A1 signal.

[1..1] PIO output enable of HIF_A1 signal.

Definition at line 14928 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a1 |

[1..1] PIO input state of HIF_A1 signal.

Definition at line 15066 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a10 |

[10..10] PIO output drive level of HIF_A10 signal.

[10..10] PIO output enable of HIF_A10 signal.

Definition at line 14937 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a10 |

[10..10] PIO input state of HIF_A10 signal.

Definition at line 15075 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a11 |

[11..11] PIO output drive level of HIF_A11 signal.

[11..11] PIO output enable of HIF_A11 signal.

Definition at line 14938 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a11 |

[11..11] PIO input state of HIF_A11 signal.

Definition at line 15076 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a12 |

[12..12] PIO output drive level of HIF_A12 signal.

[12..12] PIO output enable of HIF_A12 signal.

Definition at line 14939 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a12 |

[12..12] PIO input state of HIF_A12 signal.

Definition at line 15077 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a13 |

[13..13] PIO output drive level of HIF_A13 signal.

[13..13] PIO output enable of HIF_A13 signal.

Definition at line 14940 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a13 |

[13..13] PIO input state of HIF_A13 signal.

Definition at line 15078 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a14 |

[14..14] PIO output drive level of HIF_A14 signal.

[14..14] PIO output enable of HIF_A14 signal.

Definition at line 14941 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a14 |

[14..14] PIO input state of HIF_A14 signal.

Definition at line 15079 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a15 |

[15..15] PIO output drive level of HIF_A15 signal.

[15..15] PIO output enable of HIF_A15 signal.

Definition at line 14942 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a15 |

[15..15] PIO input state of HIF_A15 signal.

Definition at line 15080 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a16 |

[16..16] PIO output drive level of HIF_A16 signal.

[16..16] PIO output enable of HIF_A16 signal.

Definition at line 14943 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a16 |

[16..16] PIO input state of HIF_A16 signal

Definition at line 15081 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a17 |

[17..17] PIO output drive level of HIF_A17 signal.

[17..17] PIO output enable of HIF_A17 signal.

Definition at line 14944 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a17 |

[17..17] PIO input state of HIF_A17 signal

Definition at line 15082 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a2 |

[2..2] PIO output drive level of HIF_A2 signal.

[2..2] PIO output enable of HIF_A2 signal.

Definition at line 14929 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a2 |

[2..2] PIO input state of HIF_A2 signal.

Definition at line 15067 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a3 |

[3..3] PIO output drive level of HIF_A3 signal.

[3..3] PIO output enable of HIF_A3 signal.

Definition at line 14930 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a3 |

[3..3] PIO input state of HIF_A3 signal.

Definition at line 15068 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a4 |

[4..4] PIO output drive level of HIF_A4 signal.

[4..4] PIO output enable of HIF_A4 signal.

Definition at line 14931 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a4 |

[4..4] PIO input state of HIF_A4 signal.

Definition at line 15069 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a5 |

[5..5] PIO output drive level of HIF_A5 signal.

[5..5] PIO output enable of HIF_A5 signal.

Definition at line 14932 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a5 |

[5..5] PIO input state of HIF_A5 signal.

Definition at line 15070 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a6 |

[6..6] PIO output drive level of HIF_A6 signal.

[6..6] PIO output enable of HIF_A6 signal.

Definition at line 14933 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a6 |

[6..6] PIO input state of HIF_A6 signal.

Definition at line 15071 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a7 |

[7..7] PIO output drive level of HIF_A7 signal.

[7..7] PIO output enable of HIF_A7 signal.

Definition at line 14934 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a7 |

[7..7] PIO input state of HIF_A7 signal.

Definition at line 15072 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a8 |

[8..8] PIO output drive level of HIF_A8 signal.

[8..8] PIO output enable of HIF_A8 signal.

Definition at line 14935 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a8 |

[8..8] PIO input state of HIF_A8 signal.

Definition at line 15073 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_a9 |

[9..9] PIO output drive level of HIF_A9 signal.

[9..9] PIO output enable of HIF_A9 signal.

Definition at line 14936 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_a9 |

[9..9] PIO input state of HIF_A9 signal.

Definition at line 15074 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_bhen |

[25..25] PIO output drive level of HIF_BHEN signals.

[25..25] PIO output enable of HIF_BHEN signals.

Definition at line 14946 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_bhen |

[25..25] PIO input state of HIF_BHEN signal.

Definition at line 15084 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_csn |

[28..28] PIO output drive level of HIF_CSN signal.

[28..28] PIO output enable of HIF_CSN signal.

Definition at line 14949 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_csn |

[28..28] PIO input state of HIF_CSN signal.

Definition at line 15087 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d0 |

[0..0] PIO output drive level of HIF_D0 signal.

[0..0] PIO output enable of HIF_D0 signal.

Definition at line 14895 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d0 |

[0..0] PIO input state of HIF_D0 signal.

Definition at line 15038 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d1 |

[1..1] PIO output drive level of HIF_D1 signal.

[1..1] PIO output enable of HIF_D1 signal.

Definition at line 14896 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d1 |

[1..1] PIO input state of HIF_D1 signal.

Definition at line 15039 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d10 |

[10..10] PIO output drive level of HIF_D10 signal.

[10..10] PIO output enable of HIF_D10 signal.

Definition at line 14905 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d10 |

[10..10] PIO input state of HIF_D10 signal.

Definition at line 15048 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d11 |

[11..11] PIO output drive level of HIF_D11 signal.

[11..11] PIO output enable of HIF_D11 signal.

Definition at line 14906 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d11 |

[11..11] PIO input state of HIF_D11 signal.

Definition at line 15049 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d12 |

[12..12] PIO output drive level of HIF_D12 signal.

[12..12] PIO output enable of HIF_D12 signal.

Definition at line 14907 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d12 |

[12..12] PIO input state of HIF_D12 signal.

Definition at line 15050 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d13 |

[13..13] PIO output drive level of HIF_D13 signal.

[13..13] PIO output enable of HIF_D13 signal.

Definition at line 14908 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d13 |

[13..13] PIO input state of HIF_D13 signal.

Definition at line 15051 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d14 |

[14..14] PIO output drive level of HIF_D14 signal.

[14..14] PIO output enable of HIF_D14 signal.

Definition at line 14909 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d14 |

[14..14] PIO input state of HIF_D14 signal.

Definition at line 15052 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d15 |

[15..15] PIO output drive level of HIF_D15 signal.

[15..15] PIO output enable of HIF_D15 signal.

Definition at line 14910 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d15 |

[15..15] PIO input state of HIF_D15 signal.

Definition at line 15053 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d2 |

[2..2] PIO output drive level of HIF_D2 signal.

[2..2] PIO output enable of HIF_D2 signal.

Definition at line 14897 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d2 |

[2..2] PIO input state of HIF_D2 signal.

Definition at line 15040 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d3 |

[3..3] PIO output drive level of HIF_D3 signal.

[3..3] PIO output enable of HIF_D3 signal.

Definition at line 14898 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d3 |

[3..3] PIO input state of HIF_D3 signal.

Definition at line 15041 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d4 |

[4..4] PIO output drive level of HIF_D4 signal.

[4..4] PIO output enable of HIF_D4 signal.

Definition at line 14899 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d4 |

[4..4] PIO input state of HIF_D4 signal.

Definition at line 15042 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d5 |

[5..5] PIO output drive level of HIF_D5 signal.

[5..5] PIO output enable of HIF_D5 signal.

Definition at line 14900 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d5 |

[5..5] PIO input state of HIF_D5 signal.

Definition at line 15043 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d6 |

[6..6] PIO output drive level of HIF_D6 signal.

[6..6] PIO output enable of HIF_D6 signal.

Definition at line 14901 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d6 |

[6..6] PIO input state of HIF_D6 signal.

Definition at line 15044 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d7 |

[7..7] PIO output drive level of HIF_D7 signal.

[7..7] PIO output enable of HIF_D7 signal.

Definition at line 14902 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d7 |

[7..7] PIO input state of HIF_D7 signal.

Definition at line 15045 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d8 |

[8..8] PIO output drive level of HIF_D8 signal.

[8..8] PIO output enable of HIF_D8 signal.

Definition at line 14903 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d8 |

[8..8] PIO input state of HIF_D8 signal.

Definition at line 15046 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_d9 |

[9..9] PIO output drive level of HIF_D9 signal.

[9..9] PIO output enable of HIF_D9 signal.

Definition at line 14904 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_d9 |

[9..9] PIO input state of HIF_D9 signal.

Definition at line 15047 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_dirq |

[30..30] PIO output drive level of HIF_DIRQ signal.

[30..30] PIO output enable of HIF_DIRQ signal.

Definition at line 14951 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_dirq |

[30..30] PIO input state of HIF_DIRQ signal.

Definition at line 15089 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_io_cfg |

(@ 0x00000000) IO Config Register: Selects of HIF pin multiplexing. See Excel pinning sheet for details. This configuration must be set up according to external netX connection before any access to external logic. This register is protected by the netX access key mechanism; changing this register is only possible by the following sequence: 1.: read out access key from ACCESS_KEY register (ASIC_CTRL address area) 2.: write back access key to ACCESS_KEY register (ASIC_CTRL address area) 3.: write desired va

Definition at line 14752 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_io_cfg_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_mi_cfg |

[6..5] description too long, please enter short description.

Definition at line 14799 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_cfg |

(@ 0x00000004) HIF PIO Mode configuration register.

Definition at line 14838 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_cfg_b |

| __IM uint32_t hif_io_ctrl_Type::hif_pio_in0 |

(@ 0x00000018) HIF PIO Input State Register 0. IO input states can be read here regardless whether IO is used in current HIF/EXT_BUS Memory Interface configuration. HIF IO sampling behaviour can be programmed by 'in_ctrl' bits of 'hif_pio_cfg' register.

Definition at line 15030 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_in0_b |

| __IM uint32_t hif_io_ctrl_Type::hif_pio_in1 |

(@ 0x0000001C) HIF PIO Input State Register 1. IO input states can be read here regardless whether IO is used in current HIF/EXT_BUS Memory Interface configuration.

Definition at line 15059 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_in1_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_irq_arm_mask_reset |

(@ 0x0000002C) HIF PIO Interrupt Mask Reset Register for netX internal ARM. Write access with '1' resets interrupt mask bit (disables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. If bit is set, the according interrupt will activate the IRQ for netX internal ARM if asserted. Interrupt status can be cleared by writing ones to the hif_pio_irq_raw register. To release IRQ for netX internal ARM without clearing

Definition at line 15142 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_irq_arm_mask_reset_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_irq_arm_mask_set |

(@ 0x00000028) HIF PIO Interrupt Mask Register for netX internal ARM. Write access with '1' sets interrupt mask bit (enables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. If bit is set, the according interrupt will activate the IRQ for netX internal ARM. Interrupt status can be cleared by writing ones to the hif_pio_irq_raw register. To release IRQ for netX internal ARM without clearing interrupt in module,

Definition at line 15119 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_irq_arm_mask_set_b |

| __IM uint32_t hif_io_ctrl_Type::hif_pio_irq_arm_masked |

(@ 0x00000030) HIF PIO Masked Interrupt Status Register for netX internal ARM. If bit is set, if the according mask bit is set in hif_pio_irq_arm_mask-register and the according interrupt is asserted. IRQ for netX internal ARM signal is asserted if at least one bit is set here. Interrupt status can be cleared by writing ones to the hif_pio_irq_raw register. To release IRQ for netX internal ARM signal without clearing interrupt in module, reset according mask bit to 0. Note: Spikes up to 10ns will be suppre

Definition at line 15165 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_irq_arm_masked_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_irq_raw |

(@ 0x00000024) HIF PIO Raw (before masking) IRQ Status Register. If bit is set, the according interrupt is asserted. Interrupt status can be cleared by writing ones to this register. Each IRQ source can be assigned either to xPIC or to ARM (or to both) by the following registers. IRQ clearing has lower priority than IRQ set when done simultaneously. Note: Spikes up to 10ns will be suppressed by HIF PIO IRQ sample stages. Note: HIF PIO interrupt function can be configured in the hif_pio_cfg register. Note:

Definition at line 15096 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_irq_raw_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_irq_xpic_mask_reset |

(@ 0x00000038) HIF PIO Interrupt Mask Reset Register for netX internal xPIC. Write access with '1' resets interrupt mask bit (disables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. If bit is set, the according interrupt will activate the IRQ for netX internal xPIC if asserted. Interrupt status can be cleared by writing ones to the hif_pio_irq_raw register. To release IRQ for netX internal xPIC without clear

Definition at line 15211 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_irq_xpic_mask_reset_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_irq_xpic_mask_set |

(@ 0x00000034) HIF PIO Interrupt Mask Register for netX internal xPIC. Write access with '1' sets interrupt mask bit (enables interrupt request for corresponding interrupt source). Write access with '0' does not influence this bit. Read access shows actual interrupt mask. If bit is set, the according interrupt will activate the IRQ for netX internal xPIC. Interrupt status can be cleared by writing ones to the hif_pio_irq_raw register. To release IRQ for netX internal xPIC without clearing interrupt in modu

Definition at line 15188 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_irq_xpic_mask_set_b |

| __IM uint32_t hif_io_ctrl_Type::hif_pio_irq_xpic_masked |

(@ 0x0000003C) HIF PIO Masked Interrupt Status Register for netX internal xPIC. If bit is set, if the according mask bit is set in hif_pio_irq_xpic_mask-registe and the according interrupt is asserted. IRQ for netX internal xPIC signal is asserted if at least one bit is set here. Interrupt status can be cleared by writing ones to the hif_pio_irq_raw register. To release IRQ for netX internal xPIC signal without clearing interrupt in module, reset according mask bit to 0. Note: Spikes up to 10ns will be su

Definition at line 15234 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_irq_xpic_masked_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_oe0 |

(@ 0x00000010) HIF PIO Output Enable Configuration Register 0. All unused HIF signals can be used as PIOs. IOs will be driven to the output state programmed in in hif_pio_out0 register. PIO mode driving of HIF-IOs used in current HIF/EXT_BUS Memory Interface configuration is not possible. --------------------— Note: This register can be read or written by 8, 16 or 32 bit access.

Definition at line 14957 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_oe0_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_oe1 |

(@ 0x00000014) HIF PIO Output Enable Configuration Register

Definition at line 14989 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_oe1_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_out0 |

(@ 0x00000008) HIF PIO Output State Configuration Register 0. All unused HIF signals can be used as PIOs. IOs will be driven to the programmed state if appropriate enable bit is set in hif_pio_oe0 register. PIO mode driving of HIF-IOs used in current HIF/EXT_BUS Memory Interface configuration is not possible. --------------------— Note: This register can be read or written by 8, 16 or 32 bit access.

Definition at line 14884 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_out0_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_pio_out1 |

(@ 0x0000000C) HIF PIO Output State Configuration Register 1. All unused HIF signals can be used as PIOs. IOs will be driven to the programmed state if appropriate enable bit is set in hif_pio_oe1 register. PIO mode driving of HIF-IOs used in current HIF/EXT_BUS Memory Interface configuration is not possible. --------------------— Note: This register can be read or written by 8, 16 or 32 bit access.

Definition at line 14916 of file netx90_app.h.

| struct { ... } hif_io_ctrl_Type::hif_pio_out1_b |

| __IOM uint32_t hif_io_ctrl_Type::hif_rdn |

[26..26] PIO output drive level of HIF_RDN signal.

[26..26] PIO output enable of HIF_RDN signal.

Definition at line 14947 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_rdn |

[26..26] PIO input state of HIF_RDN signal.

Definition at line 15085 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_rdy |

[29..29] PIO output drive level of HIF_RDY signal.

[29..29] PIO output enable of HIF_RDY signal.

Definition at line 14950 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_rdy |

[29..29] PIO input state of HIF_RDY signal.

Definition at line 15088 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_sdclk |

[31..31] PIO output drive level of HIF_SDCLK signal.

[31..31] PIO output enable of HIF_SDCLK signal.

Definition at line 14952 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_sdclk |

[31..31] PIO input state of HIF_SDCLK signal.

Definition at line 15090 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::hif_wrn |

[27..27] PIO output drive level of HIF_WRN signal.

[27..27] PIO output enable of HIF_WRN signal.

Definition at line 14948 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::hif_wrn |

[27..27] PIO input state of HIF_WRN signal.

Definition at line 15086 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::in_ctrl |

[1..0] HIF PIO Input sampling mode. HIF input status registers hif_pio_in0,1 can be configured by programming these bits. { | Mode Function 00 pio_in registers show HIF IO states sampled at power-on-reset release. 01 HIF IO states are sampled continuously (each netX system clock cycle) 10 HIF IO states are sampling is done each system clock cycle when enable signal EN_IN (MMIO-function) level is low. 11 HIF IO states are sampling is done each system clock cycle when enable signal EN_IN (MMIO-fun

Definition at line 14841 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::irq_hif_a16 |

[1..1] HIF_A16 IRQ

Definition at line 15111 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::irq_hif_a16 |

[1..1] HIF_A16 IRQ

Definition at line 15180 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::irq_hif_a16_cfg |

[19..18] HIF_A16 IRQ input configuration For coding refer to irq_hif_dirq_cfg bit-field.

Definition at line 14859 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::irq_hif_a17 |

[2..2] HIF_A17 IRQ

Definition at line 15112 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::irq_hif_a17 |

[2..2] HIF_A17 IRQ

Definition at line 15181 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::irq_hif_a17_cfg |

[21..20] HIF_A17 IRQ input configuration For coding refer to irq_hif_dirq_cfg bit-field.

Definition at line 14861 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::irq_hif_d12 |

[0..0] HIF_D12 (DPM_SPI_DIRQ/SPM_DIRQ)

Definition at line 15110 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::irq_hif_d12 |

[0..0] HIF_D12 (DPM_SPI_DIRQ/SPM_DIRQ)

Definition at line 15179 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::irq_hif_d12_cfg |

[17..16] HIF_D12 (DPM_SPI_DIRQ/SPM_DIRQ) IRQ input configuration For coding refer to irq_hif_dirq_cfg bit-field.

Definition at line 14857 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::irq_hif_dirq |

[3..3] HIF_DIRQ IRQ

Definition at line 15113 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::irq_hif_dirq |

[3..3] HIF_DIRQ IRQ

Definition at line 15182 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::irq_hif_dirq_cfg |

[27..26] HIF_DIRQ IRQ input configuration { | Mode Function 00 low level active IRQ 01 high level active IRQ 10 falling edge active IRQ 11 rising edge active IRQ } For IRQ usage this IO should be in PIO input mode, (programmed in the 'hif_io_cfg' register or PIO-configuration registers of the DPM module). For input its PIO output enable must be programmed to '0'. Spikes on related PIO can be suppressed by 'filter_irqs' bit. Note: HIF PIO IRQs can be assigned and monitored in hif_pio_irq registers

Definition at line 14864 of file netx90_app.h.

| __IM uint32_t hif_io_ctrl_Type::RESERVED |

Definition at line 15093 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::sel_dpm_serial |

[1..1] serial (SPI) DPM mode selection (ignored if sel_hif_dpm not set). There are 2 independent serial DPM interfaces for netX90. They can be used together, e.g. one for cyclic and one for acyclic data) or stand-alone. The 1st sDPM (sDPM0) can always be used together with external memory (even 16bit mode). sDPM1 can only be used with an 8 bit MI. The pinning positions of serial DPM interfaces are provided by the main pinning table: The pinning-functions 'dpm0_spi*' represent sDPM0, pinning-functions 'dpm1_spi*'

Definition at line 14773 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::sel_dpm_serial_sph |

[2..2] serial DPM mode SPI clock phase selection (sel_hif_dpm and sel_dpm_serial must be set) 0: Serial data sampling on first serial clock edge. 1: Serial data sampling on second serial clock edge.

Definition at line 14782 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::sel_dpm_serial_spo |

[3..3] serial DPM mode SPI clock polarity selection (sel_hif_dpm and sel_dpm_serial must be set) 0: Serial clock idle state is low. 1: Serial clock idle state is high.

Definition at line 14786 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::sel_hif_a_width |

[11..8] Select HIF MI address width. Selecting smaller address bus width will allow PIO usage on related IOs when not used otherwise (e.g. as SDRAM control signals, see en_hif_sdram_mi). A0 to A11 are always enabled when the HIF MI is enabled by the hif_mi_cfg bits. Following settings are valid for 8 or 16 bit data modes. Please note: - The lower byte of the MI is located on the MII signals (refer to the pinning table). - The upper byte of the MI is located on the lower HIF_D IOs (HIF_D0..7, not on HIF_D8..15). -

Definition at line 14809 of file netx90_app.h.

| __IOM uint32_t hif_io_ctrl_Type::sel_hif_dpm |

[0..0] select DPM mode for HIF (serial or parallel) Note: For parallel DPM IO configuration use config registers in address area DPM. Note: Parallel DPM fast/service IRQ functionality (SIRQ/FIQ) on HIF_SDCLK is controlled by en_hif_sdram_mi bit Note: For parallel DPM host IRQs can be generated on HIF_DIRQ and HIF_SDCLK IOs. Note: For parallel DPM HIF PIO function muse be configured inside 'dpm_pio_cfg' registers for all HIF IOs.

Definition at line 14765 of file netx90_app.h.