|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

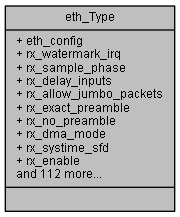

eth (eth) More...

#include <netx90_app.h>

eth (eth)

Definition at line 19433 of file netx90_app.h.

| union { ... } |

< (@ 0xFF480000) eth Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t eth_Type::bf_align0 |

[26..14] bitField alignment value for aeabi compatibility

[31..11] bitField alignment value for aeabi compatibility

[31..13] bitField alignment value for aeabi compatibility

[4..4] bitField alignment value for aeabi compatibility

[3..1] bitField alignment value for aeabi compatibility

Definition at line 19472 of file netx90_app.h.

| __IM uint32_t eth_Type::bf_align0 |

[6..5] bitField alignment value for aeabi compatibility

[26..11] bitField alignment value for aeabi compatibility

[31..13] bitField alignment value for aeabi compatibility

Definition at line 19546 of file netx90_app.h.

| __IOM uint32_t eth_Type::bf_align1 |

[31..30] bitField alignment value for aeabi compatibility

[31..9] bitField alignment value for aeabi compatibility

Definition at line 19486 of file netx90_app.h.

| __IM uint32_t eth_Type::bf_align1 |

[31..12] bitField alignment value for aeabi compatibility

Definition at line 19548 of file netx90_app.h.

| __IOM uint32_t eth_Type::data |

[31..16] Data to or from PHY register

Definition at line 19763 of file netx90_app.h.

| __IOM uint32_t eth_Type::enable |

[0..0] Enables software mode: MDC, MDO and MDOE are set by software.

Definition at line 19776 of file netx90_app.h.

| __IOM uint32_t eth_Type::eth_config |

(@ 0x00000000) ETH config register

Definition at line 19436 of file netx90_app.h.

| struct { ... } eth_Type::eth_config_b |

| __IM uint32_t eth_Type::eth_irq_masked |

(@ 0x0000002C) Masked IRQ: Shows status of masked IRQs as connected to ARM/xPIC.

Definition at line 19659 of file netx90_app.h.

| struct { ... } eth_Type::eth_irq_masked_b |

| __IOM uint32_t eth_Type::eth_irq_msk_reset |

(@ 0x00000034) IRQ mask reset: This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 19718 of file netx90_app.h.

| struct { ... } eth_Type::eth_irq_msk_reset_b |

| __IOM uint32_t eth_Type::eth_irq_msk_set |

(@ 0x00000030) IRQ mask set: The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating interrupt mask, delete old pending interrupts by writing the same value to adr_eth_irq_raw.

Definition at line 19684 of file netx90_app.h.

| struct { ... } eth_Type::eth_irq_msk_set_b |

| __IOM uint32_t eth_Type::eth_irq_raw |

(@ 0x00000028) Raw IRQ: Read access shows status of unmasked IRQs. IRQs are set automatically and reset by writing to this register: Write access with '1' resets the appropriate IRQ. Write access with '0' does not influence this bit. Write access with '1' to rx_/tx_fifo_undr/_ovfl resets RX-FIFO/TX-FIFO. Bits rx_data and tx_fifo are cleared by reading from/filling the appropriate FIFO.

Definition at line 19623 of file netx90_app.h.

| struct { ... } eth_Type::eth_irq_raw_b |

| __IOM uint32_t eth_Type::eth_miimu |

(@ 0x00000038) MDIO FSM interface controlling for netX external PHY. Note: Loopback for purpose is provided by miimu_sw register and also performed in non-software-mode when enabled. Note: Prior phy_nres-bit was removed. PHY reset must be done by register ASIC_CTRL.phy_control.

Definition at line 19747 of file netx90_app.h.

| struct { ... } eth_Type::eth_miimu_b |

| __IOM uint32_t eth_Type::eth_miimu_sw |

(@ 0x0000003C) MDIO software interface controlling for netX internal PHY. Note: Function is similar to old MIIMU unit register 'miimu_sw', however data output enable was removed as it is not necessary for MDIO interface to internal PHY (due to non-bidirectional data signal).

Definition at line 19768 of file netx90_app.h.

| struct { ... } eth_Type::eth_miimu_sw_b |

| __IM uint32_t eth_Type::eth_rx_data |

(@ 0x00000010) Data from RX-FIFO:

Definition at line 19561 of file netx90_app.h.

| struct { ... } eth_Type::eth_rx_data_b |

| __IM uint32_t eth_Type::eth_rx_len_stat |

(@ 0x00000018) Length and status information of lastly received frame

Definition at line 19582 of file netx90_app.h.

| struct { ... } eth_Type::eth_rx_len_stat_b |

| __IM uint32_t eth_Type::eth_rx_systime_ns |

(@ 0x00000020) Systime_ns sampled at start of received frame. Exact position of start of frame is defined in eth_config-systime_sfd.

Definition at line 19603 of file netx90_app.h.

| struct { ... } eth_Type::eth_rx_systime_ns_b |

| __IM uint32_t eth_Type::eth_status |

(@ 0x00000008) ETH status register:

Definition at line 19542 of file netx90_app.h.

| struct { ... } eth_Type::eth_status_b |

| __IOM uint32_t eth_Type::eth_tx_config |

(@ 0x00000004) ETH config register

Definition at line 19491 of file netx90_app.h.

| struct { ... } eth_Type::eth_tx_config_b |

| __IOM uint32_t eth_Type::eth_tx_data |

(@ 0x0000000C) Data to TX-FIFO: returns 0xdeadbeef on read

Definition at line 19553 of file netx90_app.h.

| struct { ... } eth_Type::eth_tx_data_b |

| __IOM uint32_t eth_Type::eth_tx_len |

(@ 0x00000014) Length of data inside transmitted frame (between SFD and FCS) Note: Set this value after previous frame is completely transmitted (irq-tx_frame_finished).

Definition at line 19569 of file netx90_app.h.

| struct { ... } eth_Type::eth_tx_len_b |

| __IM uint32_t eth_Type::eth_tx_systime_ns |

(@ 0x00000024) Systime_ns sampled at start of transmitted frame. Exact position of start of frame is defined in eth_tx_config-systime_sfd.

Definition at line 19613 of file netx90_app.h.

| struct { ... } eth_Type::eth_tx_systime_ns_b |

| __IOM uint32_t eth_Type::frequency |

[27..27] MII clock frequency: 1: 50MHz (use in PHY mode only) 0: 25MHz

Definition at line 19473 of file netx90_app.h.

| __IOM uint32_t eth_Type::half_duplex |

[31..31] Half Duplex Mode: 1: In half duplex mode transmission of a frame starts after the following sequence: - tx_watermark_start was reached - mii_crs became low and stayed low for tx_crs_low_cycles

Definition at line 19530 of file netx90_app.h.

| __IOM uint32_t eth_Type::hd_suppress_loopback |

[28..28] Suppress loopback in half_duplex mode: 1: don't start RX-process, if txen is active. 0: RX and TX work indepentently.

Definition at line 19475 of file netx90_app.h.

| __IOM uint32_t eth_Type::loopback |

[8..8] MDIO-data-out to data-in loopback for test purpose. 0: no loopback, MDIO-data-in comes from internal PHY. 1: loopback, MDIO-data-in comes from current MDIO-data-out. Note: Loopback can also be used in non-software-mode.

Definition at line 19782 of file netx90_app.h.

| __IOM uint32_t eth_Type::mdc |

[4..4] MDC value for software mode

Definition at line 19778 of file netx90_app.h.

| __IOM uint32_t eth_Type::mdc_period |

[3..3] MDC period: 1: 800ns 0: 400ns

Definition at line 19758 of file netx90_app.h.

| __IOM uint32_t eth_Type::mdi_ro |

[7..7] current MDI value

Definition at line 19781 of file netx90_app.h.

| __IOM uint32_t eth_Type::mdo |

[5..5] MDO value for software mode

Definition at line 19779 of file netx90_app.h.

| __IOM uint32_t eth_Type::mdoe |

[6..6] MDOE value for software mode

Definition at line 19780 of file netx90_app.h.

| __IOM uint32_t eth_Type::opmode |

[2..2] Operation mode: 1: write 0: read

Definition at line 19757 of file netx90_app.h.

| __IOM uint32_t eth_Type::phy_mode |

[29..29] PHY mode: 0: behave like an ethernet MAC, sync to external rxclk/txclk 1: behave like an ethernet PHY, generate txclk (=rxclk), signals change their function: { | rxclk: not used rxd[3:0]: data input, to be connected to txd[3:0] of MAC device rxdv: Data valid input, to be connected to txen of MAC device rxer: Error input, to be connected to txer of MAC device txclk: Clock output, to be connected to rxclk and txclk of MAC device txd[3:0]: Data output, to be connected to rxd[3:0] of

Definition at line 19477 of file netx90_app.h.

| __IOM uint32_t eth_Type::phyaddr |

[15..11] PHY address

Definition at line 19762 of file netx90_app.h.

| __IOM uint32_t eth_Type::preamble |

[1..1] Send preamble

Definition at line 19756 of file netx90_app.h.

| __IOM uint32_t eth_Type::regaddr |

[10..6] Register address

Definition at line 19761 of file netx90_app.h.

| __IM uint32_t eth_Type::RESERVED |

Definition at line 19600 of file netx90_app.h.

| __IOM uint32_t eth_Type::rta |

[5..5] Read Turn Around field: 0: one bit 1: two bits

Definition at line 19760 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_allow_jumbo_packets |

[8..8] Receive frames > 1522 bytes. If jumbo_packets are not allowed, the receive frame buffer must be 1524 bytes. Warning: Frames with len > 2047 will be received, but rx_frame_len has only 11 bit.

Definition at line 19454 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_cpu_too_slow |

[8..8] next frame started before irq_raw_rx_frame_finished was cleared

Definition at line 19646 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_cpu_too_slow |

[8..8] next frame started before irq_raw_rx_frame_finished was cleared

Definition at line 19671 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_crc_error |

[30..30] wrong RX FCS detected

Definition at line 19596 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_data |

[2..2] RX Data is available

Definition at line 19637 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_data |

[2..2] RX Data is available

Definition at line 19665 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_delay_inputs |

[7..7] Delay mii inputs (rx_d, rx_dv, rx_err, crs, col) by 1 clockcycle before sampling them. This leads to inputs fitting to sampled rxclk. Enable this in MAC mode, disable in PHY mode.

Definition at line 19450 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_dma_mode |

[11..11] Receive DMA mode: Each received frame needs 2 DMA-transfers, one for package data and one for rx_len/status. In rx_dma_mode irq_raw-rx_frame_finished is reset automatically.

Definition at line 19461 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_dribble_nibble |

[29..29] frame finished at non-even nibble count, last nibble was dropped

Definition at line 19594 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_enable |

[13..13] Enable of receive state machine: When disabled, receive state machine is reset. After enabling, receive state machine waits for rxdv going down. If rxdv is already down, proper IFG is expected.

Definition at line 19468 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_exact_preamble |

[9..9] Accept only packages with exact preamble, rx_preamble_error IRQ will be generated independant on this setting.

Definition at line 19458 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_fifo_ovfl |

[7..7] RX-FIFO overflow

Definition at line 19645 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_fifo_ovfl |

[7..7] RX-FIFO overflow

Definition at line 19670 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_fifo_undr |

[6..6] RX-FIFO underrun (debug only, can never happen in ASIC)

Definition at line 19644 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_fifo_undr |

[6..6] RX-FIFO underrun (debug only, can never happen in ASIC)

Definition at line 19669 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_fill |

[4..0] Fill-level of RX-FIFO

Definition at line 19545 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_frame_finished |

[3..3] RX frame finished: Clearing this bit tells the module, that the CPU has read rx_len_stat and the next frame can be received. In rx_dma_mode this bit is handled automatically, demask it to the CPU.

[3..3] RX frame finished

Definition at line 19638 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_frame_finished |

[3..3] RX frame finished

Definition at line 19666 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_jumbo_packet |

[28..28] rx_frame_len > 1522 detected: In case of eth_config-allow_jumbo_packe s=1, this frame was received, but rx_len will overflow at 2048. In case of eth_config-allow_jumbo_packets=0, frame is stopped after 1522, but other status information (rxerr, crc, dribble_nibble) will be checked anyway.

Definition at line 19589 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_len |

[10..0] Received data (excluding SFD and including FCS)

Definition at line 19586 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_mii_rxerr |

[31..31] external rxerr signal was active in last frame

Definition at line 19597 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_no_preamble |

[10..10] receive starts, when rxdv gets active

Definition at line 19460 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_preamble_error |

[10..10] data <> 0x5 during preamble or wrong length of preamble

Definition at line 19649 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_preamble_error |

[10..10] data <> 0x5 during preamble or wrong length of preamble

Definition at line 19674 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_sample_phase |

[6..4] clk-phase in which rxd is sampled: PHY mode (phy_mode=1): { | 0,4: sample at posedge tx_clk 1,5: sample at posedge tx_clk + 1cc 2,6: sample at posedge tx_clk + 2cc 3,7: sample at posedge tx_clk + 3cc} MAC mode (phy_mode=0): { | 0: sample at posedge rx_clk + 1cc 1: sample at posedge rx_clk

Definition at line 19441 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_short_dv |

[9..9] mii_rxdv becomes low before SFD

Definition at line 19648 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_short_dv |

[9..9] mii_rxdv becomes low before SFD

Definition at line 19673 of file netx90_app.h.

| __IM uint32_t eth_Type::rx_short_ifg |

[27..27] IFG shorter 960ns detected (preceeding this frame).

Definition at line 19588 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_systime_sfd |

[12..12] Sample systime at SFD of received frame: 1: Sample systime_ns to eth_rx_systime_ns at SFD (+constant offset) 0: Sample systime_ns to eth_rx_systime_ns when rxdv gets active (+constant offset)

Definition at line 19464 of file netx90_app.h.

| __IOM uint32_t eth_Type::rx_watermark_irq |

[3..0] Watermark for RX-FIFO, that generates interrupt This number of DWords is available inside RX-FIFO

Definition at line 19439 of file netx90_app.h.

| __IOM uint32_t eth_Type::snrdy |

[0..0] Start not ready

Definition at line 19755 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_abort_frame |

[28..26] Different abort mechanisms: 000: no abort: Transmit frame from TX-FIFO until tx_len and append correct FCS. 001: standard abort: Abort transmission, send wrong FCS, activate mii_txer. SW should keep bit active until irq-tx_frame_finished, then reset TX-FIFO. 010: abort with dribble nibble: Like standard abort, but append dribble nibble after wrong FCS (needed by some PHYs to detect error condition) SW should keep bit active until irq-tx_frame_finished, then reset TX-FIFO. 011: no FCS mode: Transmit frame f

Definition at line 19513 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_col |

[11..11] collision detected in half_duplex mode, started sending jam

Definition at line 19650 of file netx90_app.h.

| __IM uint32_t eth_Type::tx_col |

[11..11] collision detected in half_duplex mode, started sending jam

Definition at line 19675 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_crs_low_cycles |

[25..21] txclk-cycles with mii_crs low, before free carrier is detected (only used in half_duplex mode): Value range: [0,tx_min_ifg_cycles]. For details s. half_duplex mode.

Definition at line 19510 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_dma_mode |

[30..30] In tx_dma_mode tx_len comes from DMAC automatically. An extra tx_lsreq will be generated to request tx_len, before frame data is requested (and after previous frame is finished). In tx_dma_mode irq_raw-tx_frame_finished is reset automatically.

Definition at line 19525 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_fifo |

[0..0] TX-FIFO has free entries

Definition at line 19634 of file netx90_app.h.

| __IM uint32_t eth_Type::tx_fifo |

[0..0] TX-FIFO has free entries

Definition at line 19663 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_fifo_ovfl |

[5..5] TX-FIFO overflow (debug only, can never happen in ASIC)

Definition at line 19643 of file netx90_app.h.

| __IM uint32_t eth_Type::tx_fifo_ovfl |

[5..5] TX-FIFO overflow (debug only, can never happen in ASIC)

Definition at line 19668 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_fifo_undr |

[4..4] TX-FIFO underrun

Definition at line 19642 of file netx90_app.h.

| __IM uint32_t eth_Type::tx_fifo_undr |

[4..4] TX-FIFO underrun

Definition at line 19667 of file netx90_app.h.

| __IM uint32_t eth_Type::tx_fill |

[11..7] Fill-level of TX-FIFO

Definition at line 19547 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_frame_finished |

[1..1] TX frame finished: In tx_dma_mode this bit is handled automatically, demask it to the CPU.

[1..1] TX frame finished

Definition at line 19635 of file netx90_app.h.

| __IM uint32_t eth_Type::tx_frame_finished |

[1..1] TX frame finished

Definition at line 19664 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_late_col |

[12..12] late colision detected in half_duplex mode, started sending jam

Definition at line 19652 of file netx90_app.h.

| __IM uint32_t eth_Type::tx_late_col |

[12..12] late colision detected in half_duplex mode, started sending jam

Definition at line 19677 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_min_ifg_cycles |

[20..16] minimum IFG in txclk-cycles In half_duplex mode reduce value by 2 to compensate cycles for sampling of mii_crs.

Definition at line 19508 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_output_phase |

[10..8] clk-phase in which txd, txen, txer is changed at output PHY mode (phy_mode=1): { | 0,4: change output at negedge tx_clk 1,5: change output at negedge tx_clk + 1cc 2,6: change output at negedge tx_clk + 2cc 3,7: change output at negedge tx_clk + 3cc} MAC mode (phy_mode=0): { | 0: change output at posedge tx_clk + 2cc 1: change output at posedge tx_clk + 3cc 2: change output at posedge tx_clk

Definition at line 19498 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_preamble_len |

[15..11] Length of TX-preamble in nibbles (incl. SFD)

Definition at line 19507 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_systime_sfd |

[29..29] Sample systime at SFD: 1: Sample systime_ns to eth_tx_systime_ns at SFD (-constant offset) 0: Sample systime_ns to eth_tx_systime_ns when txen gets active (-constant offset)

Definition at line 19522 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_watermark_irq |

[3..0] Watermark for TX-FIFO, that generates IRQ. This number of DWords is free inside TX-FIFO

Definition at line 19494 of file netx90_app.h.

| __IOM uint32_t eth_Type::tx_watermark_start |

[7..4] Watermark for TX-FIFO, that starts transmission. This number of DWords is inside TX-FIFO

Definition at line 19496 of file netx90_app.h.

| __IOM uint32_t eth_Type::val |

[31..0] data to TX-FIFO

[10..0] To be transmitted data length (excluding SFD and excluding FCS)

Definition at line 19556 of file netx90_app.h.

| __IM uint32_t eth_Type::val |