|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

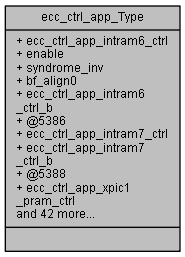

ecc_ctrl_app (ecc_ctrl_app) More...

#include <netx90_app.h>

ecc_ctrl_app (ecc_ctrl_app)

Definition at line 25770 of file netx90_app.h.

| union { ... } |

< (@ 0xFF801800) ecc_ctrl_app Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IM uint32_t ecc_ctrl_app_Type::add_addr |

[18..13] RAM readmodwrite(1) and number of master that started errorneous RAM access(5)

Definition at line 25827 of file netx90_app.h.

| __IM uint32_t ecc_ctrl_app_Type::address |

[12..0] Address of last ECC single bit error

[10..0] Address of last ECC single bit error

[12..0] Address of last ECC double bit error

[10..0] Address of last ECC double bit error

Definition at line 25826 of file netx90_app.h.

| __IOM uint32_t ecc_ctrl_app_Type::bf_align0 |

[31..8] bitField alignment value for aeabi compatibility

[31..6] bitField alignment value for aeabi compatibility

[31..4] bitField alignment value for aeabi compatibility

Definition at line 25778 of file netx90_app.h.

| __IM uint32_t ecc_ctrl_app_Type::bf_align0 |

[31..19] bitField alignment value for aeabi compatibility

[31..11] bitField alignment value for aeabi compatibility

Definition at line 25829 of file netx90_app.h.

| __IM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_intram6_addr_dbe |

(@ 0x00000020) RAM Address of ECC single bit error (DBE): This register logs the RAM address where first ECC DBE occured. This first DBE address will be stored (even in case of further DBEs) until the appropriate bit in status_sbe register was cleared. Note1: Not all RAM ECCs support error address logging, e.g. dual-port RAMs Note2: This is the real RAM address, i.e. a 32-bit address except at xMAC 64-bit RAMs or RAMs that are not directly accessible by CPU.

Definition at line 25893 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_intram6_addr_dbe_b |

| __IM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_intram6_addr_sbe |

(@ 0x00000010) RAM Address of ECC single bit error (SBE): This register logs the RAM address where first ECC SBE occured. This first SBE address will be stored (even in case of further SBEs) until the appropriate bit in status_sbe register was cleared. Note1: Not all RAM ECCs support error address logging, e.g. dual-port RAMs Note2: This is the real RAM address, i.e. a 32-bit address except at xMAC 64-bit RAMs or RAMs that are not directly accessible by CPU.

Definition at line 25813 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_intram6_addr_sbe_b |

| __IOM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_intram6_ctrl |

(@ 0x00000000) INTRAM6 syndrome manipulation register

Definition at line 25773 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_intram6_ctrl_b |

| __IM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_intram7_addr_dbe |

(@ 0x00000024) RAM Address of ECC single bit error (DBE): This register logs the RAM address where first ECC DBE occured. This first DBE address will be stored (even in case of further DBEs) until the appropriate bit in status_sbe register was cleared. Note1: Not all RAM ECCs support error address logging, e.g. dual-port RAMs Note2: This is the real RAM address, i.e. a 32-bit address except at xMAC 64-bit RAMs or RAMs that are not directly accessible by CPU.

Definition at line 25914 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_intram7_addr_dbe_b |

| __IM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_intram7_addr_sbe |

(@ 0x00000014) RAM Address of ECC single bit error (SBE): This register logs the RAM address where first ECC SBE occured. This first SBE address will be stored (even in case of further SBEs) until the appropriate bit in status_sbe register was cleared. Note1: Not all RAM ECCs support error address logging, e.g. dual-port RAMs Note2: This is the real RAM address, i.e. a 32-bit address except at xMAC 64-bit RAMs or RAMs that are not directly accessible by CPU.

Definition at line 25834 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_intram7_addr_sbe_b |

| __IOM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_intram7_ctrl |

(@ 0x00000004) INTRAM7 syndrome manipulation register

Definition at line 25783 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_intram7_ctrl_b |

| __IOM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_status_dbe |

(@ 0x00000034) ECC status DBE: This register collects double bit error (DBE) status information. In case of ECC DBE, a bit of the appropriate RAM in this register will be set. Bits can be reset by writing '1' to the apprpriate bit position (write to clear). If a SBE or DBE bit is set, IRQ signal will be asserted. Note: No mask register is required, as error correction can be enabled for each RAM separately.

Definition at line 25993 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_status_dbe_b |

| __IOM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_status_sbe |

(@ 0x00000030) ECC status SBE: This register collects single bit error (SBE) status information. In case of ECC SBE, a bit in this register will be set. Bits can be reset by writing '1' to the apprpriate bit position (write to clear). If a SBE or DBE bit is set, IRQ signal will be asserted. Note: No mask register is required, as error correction can be enabled for each RAM separately.

Definition at line 25973 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_status_sbe_b |

| __IM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_dram_addr_dbe |

(@ 0x0000002C) RAM Address of ECC single bit error (DBE): This register logs the RAM address where first ECC DBE occured. This first DBE address will be stored (even in case of further DBEs) until the appropriate bit in status_sbe register was cleared. Note1: Not all RAM ECCs support error address logging, e.g. dual-port RAMs Note2: This is the real RAM address, i.e. a 32-bit address except at xMAC 64-bit RAMs or RAMs that are not directly accessible by CPU.

Definition at line 25954 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_dram_addr_dbe_b |

| __IM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_dram_addr_sbe |

(@ 0x0000001C) RAM Address of ECC single bit error (SBE): This register logs the RAM address where first ECC SBE occured. This first SBE address will be stored (even in case of further SBEs) until the appropriate bit in status_sbe register was cleared. Note1: Not all RAM ECCs support error address logging, e.g. dual-port RAMs Note2: This is the real RAM address, i.e. a 32-bit address except at xMAC 64-bit RAMs or RAMs that are not directly accessible by CPU.

Definition at line 25874 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_dram_addr_sbe_b |

| __IOM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_dram_ctrl |

(@ 0x0000000C) XPIC1_DRAM syndrome manipulation register

Definition at line 25803 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_dram_ctrl_b |

| __IM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_pram_addr_dbe |

(@ 0x00000028) RAM Address of ECC single bit error (DBE): This register logs the RAM address where first ECC DBE occured. This first DBE address will be stored (even in case of further DBEs) until the appropriate bit in status_sbe register was cleared. Note1: Not all RAM ECCs support error address logging, e.g. dual-port RAMs Note2: This is the real RAM address, i.e. a 32-bit address except at xMAC 64-bit RAMs or RAMs that are not directly accessible by CPU.

Definition at line 25935 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_pram_addr_dbe_b |

| __IM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_pram_addr_sbe |

(@ 0x00000018) RAM Address of ECC single bit error (SBE): This register logs the RAM address where first ECC SBE occured. This first SBE address will be stored (even in case of further SBEs) until the appropriate bit in status_sbe register was cleared. Note1: Not all RAM ECCs support error address logging, e.g. dual-port RAMs Note2: This is the real RAM address, i.e. a 32-bit address except at xMAC 64-bit RAMs or RAMs that are not directly accessible by CPU.

Definition at line 25855 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_pram_addr_sbe_b |

| __IOM uint32_t ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_pram_ctrl |

(@ 0x00000008) XPIC1_PRAM syndrome manipulation register

Definition at line 25793 of file netx90_app.h.

| struct { ... } ecc_ctrl_app_Type::ecc_ctrl_app_xpic1_pram_ctrl_b |

| __IOM uint32_t ecc_ctrl_app_Type::enable |

[0..0] enable ECC

Definition at line 25776 of file netx90_app.h.

| __IOM uint32_t ecc_ctrl_app_Type::intram6 |

[0..0] INTRAM6 Single Bit Error occured

[0..0] INTRAM6 Double Bit Error occured

Definition at line 25984 of file netx90_app.h.

| __IOM uint32_t ecc_ctrl_app_Type::intram7 |

[1..1] INTRAM7 Single Bit Error occured

[1..1] INTRAM7 Double Bit Error occured

Definition at line 25985 of file netx90_app.h.

| __IOM uint32_t ecc_ctrl_app_Type::syndrome_inv |

[7..1] Inverts syndrome bits for ECC testing

[5..1] Inverts syndrome bits for ECC testing

Definition at line 25777 of file netx90_app.h.

| __IOM uint32_t ecc_ctrl_app_Type::xpic1_dram |

[3..3] XPIC1_DRAM Single Bit Error occured

[3..3] XPIC1_DRAM Double Bit Error occured

Definition at line 25987 of file netx90_app.h.

| __IOM uint32_t ecc_ctrl_app_Type::xpic1_pram |

[2..2] XPIC1_PRAM Single Bit Error occured

[2..2] XPIC1_PRAM Double Bit Error occured

Definition at line 25986 of file netx90_app.h.