|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

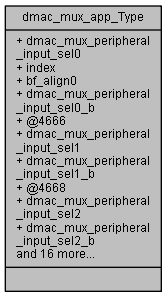

dmac_mux_app (dmac_mux_app) More...

#include <netx90_app.h>

dmac_mux_app (dmac_mux_app)

Definition at line 20175 of file netx90_app.h.

| union { ... } |

< (@ 0xFF801000) dmac_mux_app Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t dmac_mux_app_Type::bf_align0 |

[31..6] bitField alignment value for aeabi compatibility

Definition at line 20194 of file netx90_app.h.

| __IOM uint32_t dmac_mux_app_Type::dmac_mux_peripheral_input_sel0 |

(@ 0x00000000) Peripheral input select for DMAC input channel 0 This register configures which peripheral should be connected to DMAC's input channel 0. Note: This should not be changed while any of the DMA channels are performing DMA transfers.

Definition at line 20178 of file netx90_app.h.

| struct { ... } dmac_mux_app_Type::dmac_mux_peripheral_input_sel0_b |

| __IOM uint32_t dmac_mux_app_Type::dmac_mux_peripheral_input_sel1 |

(@ 0x00000004) Peripheral input select for DMAC input channel 1 This register configures which peripheral should be connected to DMAC's input channel

Definition at line 20199 of file netx90_app.h.

| struct { ... } dmac_mux_app_Type::dmac_mux_peripheral_input_sel1_b |

| __IOM uint32_t dmac_mux_app_Type::dmac_mux_peripheral_input_sel2 |

(@ 0x00000008) Peripheral input select for DMAC input channel 2 This register configures which peripheral should be connected to DMAC's input channel

Definition at line 20216 of file netx90_app.h.

| struct { ... } dmac_mux_app_Type::dmac_mux_peripheral_input_sel2_b |

| __IOM uint32_t dmac_mux_app_Type::dmac_mux_peripheral_input_sel3 |

(@ 0x0000000C) Peripheral input select for DMAC input channel 3 This register configures which peripheral should be connected to DMAC's input channel

Definition at line 20233 of file netx90_app.h.

| struct { ... } dmac_mux_app_Type::dmac_mux_peripheral_input_sel3_b |

| __IOM uint32_t dmac_mux_app_Type::dmac_mux_peripheral_input_sel4 |

(@ 0x00000010) Peripheral input select for DMAC input channel 4 This register configures which peripheral should be connected to DMAC's input channel

Definition at line 20250 of file netx90_app.h.

| struct { ... } dmac_mux_app_Type::dmac_mux_peripheral_input_sel4_b |

| __IOM uint32_t dmac_mux_app_Type::dmac_mux_peripheral_input_sel5 |

(@ 0x00000014) Peripheral input select for DMAC input channel 5 This register configures which peripheral should be connected to DMAC's input channel

Definition at line 20267 of file netx90_app.h.

| struct { ... } dmac_mux_app_Type::dmac_mux_peripheral_input_sel5_b |

| __IOM uint32_t dmac_mux_app_Type::dmac_mux_peripheral_input_sel6 |

(@ 0x00000018) Peripheral input select for DMAC input channel 6 This register configures which peripheral should be connected to DMAC's input channel

Definition at line 20284 of file netx90_app.h.

| struct { ... } dmac_mux_app_Type::dmac_mux_peripheral_input_sel6_b |

| __IOM uint32_t dmac_mux_app_Type::dmac_mux_peripheral_input_sel7 |

(@ 0x0000001C) Peripheral input select for DMAC input channel 7 This register configures which peripheral should be connected to DMAC's input channel

Definition at line 20301 of file netx90_app.h.

| struct { ... } dmac_mux_app_Type::dmac_mux_peripheral_input_sel7_b |

| __IOM uint32_t dmac_mux_app_Type::index |

[5..0] Index of the peripheral to be connected to DMAC's input channel 0. Default connected peripheral: uart_app_rx { | Number Peripheral 0 uart_rx 1 uart_tx 2 uart_app_rx (default on DMAC input channel 0) 3 uart_app_tx (default on DMAC input channel 1) 4 i2c_app_master (default on DMAC input channel 2) 5 i2c_app_slave (default on DMAC input channel 3) 6 spi0_app_rx (default on DMAC input channel 4) 7 spi0_app_tx (default on DMAC input channel 5) 8 sp

[5..0] Index of the peripheral to be connected to DMAC's input channel 1. Default connected peripheral: uart_app_tx For a list of available peripheral indices, see dmac_mux_peripheral_input_sel [5..0] Index of the peripheral to be connected to DMAC's input channel 2. Default connected peripheral: i2c_app_master For a list of available peripheral indices, see dmac_mux_peripheral_input sel0.

[5..0] Index of the peripheral to be connected to DMAC's input channel 3. Default connected peripheral: i2c_app_slave For a list of available peripheral indices, see dmac_mux_peripheral_input sel0.

[5..0] Index of the peripheral to be connected to DMAC's input channel 4. Default connected peripheral: spi0_app_rx For a list of available peripheral indices, see dmac_mux_peripheral_input_sel [5..0] Index of the peripheral to be connected to DMAC's input channel 5. Default connected peripheral: spi0_app_tx For a list of available peripheral indices, see dmac_mux_peripheral_input_sel [5..0] Index of the peripheral to be connected to DMAC's input channel 6. Default connected peripheral: uart_rx For a list of available peripheral indices, see dmac_mux_peripheral_input_sel0.

[5..0] Index of the peripheral to be connected to DMAC's input channel 7. Default connected peripheral: uart_rx For a list of available peripheral indices, see dmac_mux_peripheral_input_sel0.

Definition at line 20186 of file netx90_app.h.