|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

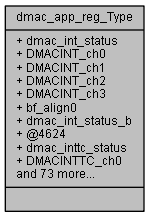

dmac_app_reg (dmac_app_reg) More...

#include <netx90_app.h>

dmac_app_reg (dmac_app_reg)

Definition at line 19959 of file netx90_app.h.

| union { ... } |

< (@ 0xFF800800) dmac_app_reg Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IM uint32_t dmac_app_reg_Type::bf_align0 |

[31..4] bitField alignment value for aeabi compatibility

Definition at line 19973 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::bf_align0 |

[31..4] bitField alignment value for aeabi compatibility

Definition at line 20005 of file netx90_app.h.

| __IOM uint32_t dmac_app_reg_Type::bf_align0 |

[31..16] bitField alignment value for aeabi compatibility

[31..1] bitField alignment value for aeabi compatibility

Definition at line 20093 of file netx90_app.h.

| __IOM uint32_t dmac_app_reg_Type::DIS_SYNC |

[15..0] Disable sync register peripheral requests.

Definition at line 20158 of file netx90_app.h.

| __IOM uint32_t dmac_app_reg_Type::dmac_config |

(@ 0x00000030) configuration register

Definition at line 20134 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_config_b |

| __IM uint32_t dmac_app_reg_Type::dmac_enabled_channel |

(@ 0x0000001C) channel enable register

Definition at line 20074 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_enabled_channel_b |

| __IM uint32_t dmac_app_reg_Type::dmac_int_status |

(@ 0x00000000) interrupt status register

Definition at line 19962 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_int_status_b |

| __OM uint32_t dmac_app_reg_Type::dmac_interr_clear |

(@ 0x00000010) interrupt error clear register

Definition at line 20026 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_interr_clear_b |

| __IM uint32_t dmac_app_reg_Type::dmac_interr_status |

(@ 0x0000000C) interrupt error status register

Definition at line 20010 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_interr_status_b |

| __OM uint32_t dmac_app_reg_Type::dmac_inttc_clear |

(@ 0x00000008) interrupt terminal count clear register

Definition at line 19994 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_inttc_clear_b |

| __IM uint32_t dmac_app_reg_Type::dmac_inttc_status |

(@ 0x00000004) interrupt terminal count status register

Definition at line 19978 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_inttc_status_b |

| __IM uint32_t dmac_app_reg_Type::dmac_rawinterr_status |

(@ 0x00000018) raw interrupt error status register

Definition at line 20058 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_rawinterr_status_b |

| __IM uint32_t dmac_app_reg_Type::dmac_rawinttc_status |

(@ 0x00000014) raw interrupt terminal count status register

Definition at line 20042 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_rawinttc_status_b |

| __IOM uint32_t dmac_app_reg_Type::dmac_softb_req |

(@ 0x00000020) software burst request register

Definition at line 20086 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_softb_req_b |

| __IOM uint32_t dmac_app_reg_Type::dmac_softlb_req |

(@ 0x00000028) software last burst request register

Definition at line 20110 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_softlb_req_b |

| __IOM uint32_t dmac_app_reg_Type::dmac_softls_req |

(@ 0x0000002C) software last single request register

Definition at line 20122 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_softls_req_b |

| __IOM uint32_t dmac_app_reg_Type::dmac_softs_req |

(@ 0x00000024) software single request register

Definition at line 20098 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_softs_req_b |

| __IOM uint32_t dmac_app_reg_Type::dmac_sync |

(@ 0x00000034) sync register DMA synchronization logic for DMA request signals enabled or disabled A 1'b0 bit indicates that the synchronization logic for the DMACBREQ[15:0], DMACSREQ[15:0], DMACLBREQ[15:0], and DMACLSREQ[15:0] request signals is enabled. A HIGH bit indicates that the synchronization logic is disabled. Note: Within the netX system all peripherals and the DMAC are running in the same clock-domain. Therefore, it is recommended to disable the synchronisation for all channels (i.e. write 0xfff

Definition at line 20144 of file netx90_app.h.

| struct { ... } dmac_app_reg_Type::dmac_sync_b |

| __IOM uint32_t dmac_app_reg_Type::DMACENABLE |

[0..0] DMAC enable: 0 = disabled 1 = enabled. This bit is reset to 0. Disabling the DMAC reduces power consumption.

Definition at line 20137 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACENABLEDCHNS_ch0 |

[0..0] Status DMA channel 0 enable

Definition at line 20077 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACENABLEDCHNS_ch1 |

[1..1] Status DMA channel 1 enable

Definition at line 20078 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACENABLEDCHNS_ch2 |

[2..2] Status DMA channel 2 enable

Definition at line 20079 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACENABLEDCHNS_ch3 |

[3..3] Status DMA channel 3 enable

Definition at line 20080 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINT_ch0 |

[0..0] Status of DMA channel 0 - interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 19965 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINT_ch1 |

[1..1] Status of DMA channel 1 - interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 19967 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINT_ch2 |

[2..2] Status of DMA channel 2 - interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 19969 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINT_ch3 |

[3..3] Status of DMA channel 3 - interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 19971 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINTERR_ch0 |

[0..0] Status of DMA channel 0 - error interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 20013 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINTERR_ch1 |

[1..1] Status of DMA channel 1 - error interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 20015 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINTERR_ch2 |

[2..2] Status of DMA channel 2 - error interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 20017 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINTERR_ch3 |

[3..3] Status of DMA channel 3 - error interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 20019 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::DMACINTERRCLR_ch0 |

[0..0] Writing a 1'b1 Bit clears the error interrupt of the specific channel 0 ,1'b0 have no effect.

Definition at line 20029 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::DMACINTERRCLR_ch1 |

[1..1] Writing a 1'b1 Bit clears the error interrupt of the specific channel 1 ,1'b0 have no effect.

Definition at line 20031 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::DMACINTERRCLR_ch2 |

[2..2] Writing a 1'b1 Bit clears the error interrupt of the specific channel 2 ,1'b0 have no effect.

Definition at line 20033 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::DMACINTERRCLR_ch3 |

[3..3] Writing a 1'b1 Bit clears the error interrupt of the specific channel 3 ,1'b0 have no effect.

Definition at line 20035 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINTTC_ch0 |

[0..0] Status of DMA channel 0 - terminal count interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 19981 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINTTC_ch1 |

[1..1] Status of DMA channel 1 - terminal count interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 19983 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINTTC_ch2 |

[2..2] Status of DMA channel 2 - terminal count interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 19985 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACINTTC_ch3 |

[3..3] Status of DMA channel 3 - terminal count interrupt after masking. 1'b1 indicates an active interrupt request.

Definition at line 19987 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::DMACINTTCCLR_ch0 |

[0..0] Writing a 1'b1 Bit clears the terminal count interrupt of the specific channel 0 ,1'b0 have no effect.

Definition at line 19997 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::DMACINTTCCLR_ch1 |

[1..1] Writing a 1'b1 Bit clears the terminal count interrupt of the specific channel 1 ,1'b0 have no effect.

Definition at line 19999 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::DMACINTTCCLR_ch2 |

[2..2] Writing a 1'b1 Bit clears the terminal count interrupt of the specific channel 2 ,1'b0 have no effect.

Definition at line 20001 of file netx90_app.h.

| __OM uint32_t dmac_app_reg_Type::DMACINTTCCLR_ch3 |

[3..3] Writing a 1'b1 Bit clears the terminal count interrupt of the specific channel 3 ,1'b0 have no effect.

Definition at line 20003 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACRAWINTERR_ch0 |

[0..0] Status of DMA channel 0 - error interrupt prior to masking. 1'b1 indicates an active interrupt request.

Definition at line 20061 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACRAWINTERR_ch1 |

[1..1] Status of DMA channel 1 - error interrupt prior to masking. 1'b1 indicates an active interrupt request.

Definition at line 20063 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACRAWINTERR_ch2 |

[2..2] Status of DMA channel 2 - error interrupt prior to masking. 1'b1 indicates an active interrupt request.

Definition at line 20065 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACRAWINTERR_ch3 |

[3..3] Status of DMA channel 3 - error interrupt prior to masking. 1'b1 indicates an active interrupt request.

Definition at line 20067 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACRAWINTTC_ch0 |

[0..0] Status of DMA channel 0 - terminal count interrupt prior to masking. 1'b1 indicates an active interrupt request.

Definition at line 20045 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACRAWINTTC_ch1 |

[1..1] Status of DMA channel 1 - terminal count interrupt prior to masking. 1'b1 indicates an active interrupt request.

Definition at line 20047 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACRAWINTTC_ch2 |

[2..2] Status of DMA channel 2 - terminal count interrupt prior to masking. 1'b1 indicates an active interrupt request.

Definition at line 20049 of file netx90_app.h.

| __IM uint32_t dmac_app_reg_Type::DMACRAWINTTC_ch3 |

[3..3] Status of DMA channel 3 - terminal count interrupt prior to masking. 1'b1 indicates an active interrupt request.

Definition at line 20051 of file netx90_app.h.

| __IOM uint32_t dmac_app_reg_Type::DMACSoftBReq |

[15..0] Software burst request. A DMA request can be generated for each source by writing a 1'b1 to the corresponding register bit. Reading the register indicates which sources are requesting DMA burst transfers.

Definition at line 20089 of file netx90_app.h.

| __IOM uint32_t dmac_app_reg_Type::DMACSoftLBReq |

[15..0] Software last burst request. A DMA request can be generated for each source by writing a 1'b1 to the corresponding register bit. Reading the register indicates which sources are requesting DMA last burst transfers.

Definition at line 20113 of file netx90_app.h.

| __IOM uint32_t dmac_app_reg_Type::DMACSoftLSReq |

[15..0] Software last single request. A DMA request can be generated for each source by writing a 1'b1 to the corresponding register bit. Reading the register indicates which sources are requesting DMA last single transfers.

Definition at line 20125 of file netx90_app.h.

| __IOM uint32_t dmac_app_reg_Type::DMACSoftSReq |

[15..0] Software single request. A DMA request can be generated for each source by writing a 1'b1 to the corresponding register bit. Reading the register indicates which sources are requesting DMA single transfers.

Definition at line 20101 of file netx90_app.h.