|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

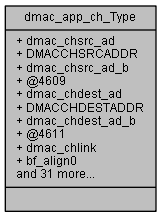

dmac_app_ch0 (dmac_app_ch) More...

#include <netx90_app.h>

Data Fields | |

| union { | |

| __IOM uint32_t * dmac_chsrc_ad | |

| struct { | |

| __IOM uint32_t DMACCHSRCADDR: 32 | |

| } dmac_chsrc_ad_b | |

| }; | |

| union { | |

| __IOM uint32_t * dmac_chdest_ad | |

| struct { | |

| __IOM uint32_t DMACCHDESTADDR: 32 | |

| } dmac_chdest_ad_b | |

| }; | |

| union { | |

| __IOM uint32_t * dmac_chlink | |

| struct { | |

| __IOM uint32_t bf_align0: 2 | |

| __IOM uint32_t LLIADDR: 30 | |

| } dmac_chlink_b | |

| }; | |

| union { | |

| __IOM uint32_t dmac_chctrl | |

| struct { | |

| __IOM uint32_t TransferSize: 12 | |

| __IOM uint32_t SBSize: 3 | |

| __IOM uint32_t DBSize: 3 | |

| __IOM uint32_t SWidth: 3 | |

| __IOM uint32_t DWidth: 3 | |

| __IOM uint32_t ARM_EQ: 1 | |

| __IOM uint32_t bf_align0: 1 | |

| __IOM uint32_t SI: 1 | |

| __IOM uint32_t DI: 1 | |

| __IOM uint32_t Prot: 3 | |

| __IOM uint32_t I: 1 | |

| } dmac_chctrl_b | |

| }; | |

| union { | |

| __IOM uint32_t dmac_chcfg | |

| struct { | |

| __IOM uint32_t E: 1 | |

| __IOM uint32_t SrcPeripheral: 4 | |

| __IOM uint32_t bf_align0: 1 | |

| __IOM uint32_t DestPeripheral: 4 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t FlowCntrl: 3 | |

| __IOM uint32_t IE: 1 | |

| __IOM uint32_t ITC: 1 | |

| __IOM uint32_t L: 1 | |

| __IOM uint32_t A: 1 | |

| __IOM uint32_t H: 1 | |

| __IOM uint32_t bf_align2: 13 | |

| } dmac_chcfg_b | |

| }; | |

| __IM uint32_t | RESERVED [3] |

dmac_app_ch0 (dmac_app_ch)

Definition at line 19802 of file netx90_app.h.

| union { ... } |

< (@ 0xFF800100) dmac_app_ch Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t dmac_app_ch_Type::A |

[17..17] Active: 0 = there is no data in the FIFO of the channel 1 = the FIFO of the channel has data. (ro) This value can be used with the Halt and Channel Enable bits to cleanly disable a DMA channel.

Definition at line 19933 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::ARM_EQ |

[24..24] Set equal behaviour to arm implementation This bit should always be set to 1 (default of 0 is from historical reasons). This bit changes 2 behavioural details: 1. ARM_EQ=1: ignore single requests in DMA-controlled Memory-to-Peripheral accesses. ARM_EQ=0: handle single requests like burst requests (in this case DBSize should be 1 access). Note: In DMA-controlled Memory-to-Peripheral mode only burst request signals are allowed. The behaviour of single requests (from peripheral to DMAC) is not defined. Module

Definition at line 19871 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::bf_align0 |

[1..0] bitField alignment value for aeabi compatibility

[25..25] bitField alignment value for aeabi compatibility

[5..5] bitField alignment value for aeabi compatibility

Definition at line 19824 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::bf_align1 |

[10..10] bitField alignment value for aeabi compatibility

Definition at line 19918 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::bf_align2 |

[31..19] bitField alignment value for aeabi compatibility

Definition at line 19941 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::DBSize |

[17..15] Destination burst size: Indicates the number of transfers which make up a destination burst transfer request. This value must be set to the burst size of the destination peripheral, or if the destination is memory, to the memory boundary size. The burst size is the amount of data that is transferred when the DMACxBREQ signal goes active in the destination peripheral. The burst size is not related to the AHB HBURST signal. Note: If flow controller is DMAC and destination is a peripheral, only bursts are tra

Definition at line 19852 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::DestPeripheral |

[9..6] Destination peripheral. This value selects the DMA destination request peripheral. This field is ignored if the destination of the transfer is to memory. For mapping of peripheral to value see 'SrcPeripheral' bit-field in this register.

Definition at line 19914 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::DI |

[27..27] Destination increment. When set the destination address is incremented after each transfer.

Definition at line 19883 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::dmac_chcfg |

(@ 0x00000010) channel configuration registers

Definition at line 19893 of file netx90_app.h.

| struct { ... } dmac_app_ch_Type::dmac_chcfg_b |

| __IOM uint32_t dmac_app_ch_Type::dmac_chctrl |

(@ 0x0000000C) channel control registers

Definition at line 19831 of file netx90_app.h.

| struct { ... } dmac_app_ch_Type::dmac_chctrl_b |

| __IOM uint32_t* dmac_app_ch_Type::dmac_chdest_ad |

(@ 0x00000004) channel destination address registers

Definition at line 19813 of file netx90_app.h.

| struct { ... } dmac_app_ch_Type::dmac_chdest_ad_b |

| __IOM uint32_t* dmac_app_ch_Type::dmac_chlink |

(@ 0x00000008) channel linked list item register

Definition at line 19821 of file netx90_app.h.

| struct { ... } dmac_app_ch_Type::dmac_chlink_b |

| __IOM uint32_t* dmac_app_ch_Type::dmac_chsrc_ad |

(@ 0x00000000) channel source address registers

Definition at line 19805 of file netx90_app.h.

| struct { ... } dmac_app_ch_Type::dmac_chsrc_ad_b |

| __IOM uint32_t dmac_app_ch_Type::DMACCHDESTADDR |

[31..0] DMA destination address

Definition at line 19816 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::DMACCHSRCADDR |

[31..0] DMA source address

Definition at line 19808 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::DWidth |

[23..21] Destination transfer width: The source and destination widths can be different from each other. The hardware automatically packs and unpacks the data as required. _________________________ bit_value data_width ----------------------— 000 8 bit 001 16 bit 010 32 bit =========================

Definition at line 19866 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::E |

[0..0] Channel enable. Reading this bit indicates whether a channel is currently enabled or disabled: 0 = channel disabled 1 = channel enabled. The Channel Enable bit status can also be found by reading the DMACEnbldChns register. A channel is enabled by setting this bit. Before enabling a single channel the DMA controller must be enabled globally by setting the DMACENABLE bit in the dmac_config register. Enabling a channel while the controller is disabled leads to undefined behaviour. A channel can be disabled b

Definition at line 19896 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::FlowCntrl |

[13..11] Flow control and transfer type. This value is used to indicate the flow controller and transfer type. The flow controller can be the DMAC, the source peripheral, or the destination peripheral. The transfer type can be either memory-to-memory, memory-to-peripheral, peripheral-to-memory, or peripheral-to-peripheral. ____________________________________________

Definition at line 19919 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::H |

[18..18] Halt: 0 = allow DMA requests 1 = ignore further source DMA requests. The contents of the channels FIFO are drained. This value can be used with the Active and Channel Enable bits to cleanly disable a DMA channel.

Definition at line 19937 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::I |

[31..31] Terminal count interrupt enable bit. It controls whether the current LLI is expected to trigger the terminal count interrupt.

Definition at line 19886 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::IE |

[14..14] Interrupt error mask. When cleared this bit masks out the error interrupt of the relevant channel.

Definition at line 19927 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::ITC |

[15..15] Terminal count interrupt mask. When cleared this bit masks out the terminal count interrupt of the relevant channel.

Definition at line 19929 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::L |

[16..16] Lock. When set this bit enables locked transfers.

Definition at line 19932 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::LLIADDR |

[31..2] Linked list item. Bits [31:2] of the address for the next LLI. Address bits [1:0] are 0.

Definition at line 19825 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::Prot |

[30..28] Protection.

Definition at line 19885 of file netx90_app.h.

| __IM uint32_t dmac_app_ch_Type::RESERVED[3] |

Definition at line 19944 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::SBSize |

[14..12] Source burst size: Indicates the number of transfers which make up a source burst. This value must be set to the burst size of the source peripheral, or if the source is memory, to the memory boundary size. The burst size is the amount of data that is transferred when the DMACxBREQ signal goes active in the source peripheral. The burst size is not related to the AHB HBURST signal. ___________________________ ____ bit_value burst_transfer_size -----------------------------— 000 1 001 4

Definition at line 19843 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::SI |

[26..26] Source increment. When set the source address is incremented after each transfer.

Definition at line 19881 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::SrcPeripheral |

[4..1] Source peripheral. This value selects the DMA source request peripheral. This field is ignored if the source of the transfer is from memory. Note: The mapping of peripherals to App-side DMAC inputs is done within the DMAC_MUX_APP module. See 'dmac_mux_peripheral_input_sel*' registers for default mapping / current mapping. { | | value Com-side App-side 0 uart_rx dmac_mux_peripheral_input_sel0 1 uart_tx dmac_mux_peripheral_input_sel1 2

Definition at line 19905 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::SWidth |

[20..18] Source transfer width: The source and destination widths can be different from each other. The hardware automatically packs and unpacks the data as required. _________________________ bit_value data_width ----------------------— 000 8 bit 001 16 bit 010 32 bit =========================

Definition at line 19861 of file netx90_app.h.

| __IOM uint32_t dmac_app_ch_Type::TransferSize |

[11..0] Transfer size: For writes, this field indicates the number of (Source width) transfers to perform when the DMAC is the flow controller. For reads, the transfer size indicates the number of transfers completed on the destination bus. Reading the register when the channel is active does not give useful information, as by the time that the software has processed the value read, the channel might have progressed. It is intended to be used only when a channel is enabled and then disabled. If the DMAC controller

Definition at line 19834 of file netx90_app.h.