|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

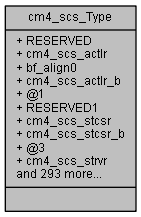

cm4_scs (cm4_scs) More...

#include <netx90_app.h>

Data Fields | |

| __IM uint32_t | RESERVED [2] |

| union { | |

| __IOM uint32_t cm4_scs_actlr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_actlr_b | |

| }; | |

| __IM uint32_t | RESERVED1 |

| union { | |

| __IOM uint32_t cm4_scs_stcsr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_stcsr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_strvr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_strvr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_stcvr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_stcvr_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_stcr | |

| struct { | |

| __IM uint32_t bf_align0: 32 | |

| } cm4_scs_stcr_b | |

| }; | |

| __IM uint32_t | RESERVED2 [56] |

| union { | |

| __IOM uint32_t cm4_scs_nvic_iser0 | |

| struct { | |

| __IOM uint32_t setena: 32 | |

| } cm4_scs_nvic_iser0_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_iser1 | |

| struct { | |

| __IOM uint32_t setena: 32 | |

| } cm4_scs_nvic_iser1_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_iser2 | |

| struct { | |

| __IOM uint32_t setena: 32 | |

| } cm4_scs_nvic_iser2_b | |

| }; | |

| __IM uint32_t | RESERVED3 [29] |

| union { | |

| __IOM uint32_t cm4_scs_nvic_icer0 | |

| struct { | |

| __IOM uint32_t clrena: 32 | |

| } cm4_scs_nvic_icer0_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_icer1 | |

| struct { | |

| __IOM uint32_t clrena: 32 | |

| } cm4_scs_nvic_icer1_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_icer2 | |

| struct { | |

| __IOM uint32_t clrena: 32 | |

| } cm4_scs_nvic_icer2_b | |

| }; | |

| __IM uint32_t | RESERVED4 [29] |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ispr0 | |

| struct { | |

| __IOM uint32_t setpend: 32 | |

| } cm4_scs_nvic_ispr0_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ispr1 | |

| struct { | |

| __IOM uint32_t setpend: 32 | |

| } cm4_scs_nvic_ispr1_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ispr2 | |

| struct { | |

| __IOM uint32_t setpend: 32 | |

| } cm4_scs_nvic_ispr2_b | |

| }; | |

| __IM uint32_t | RESERVED5 [29] |

| union { | |

| __IOM uint32_t cm4_scs_nvic_icpr0 | |

| struct { | |

| __IOM uint32_t clrpend: 32 | |

| } cm4_scs_nvic_icpr0_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_icpr1 | |

| struct { | |

| __IOM uint32_t clrpend: 32 | |

| } cm4_scs_nvic_icpr1_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_icpr2 | |

| struct { | |

| __IOM uint32_t clrpend: 32 | |

| } cm4_scs_nvic_icpr2_b | |

| }; | |

| __IM uint32_t | RESERVED6 [29] |

| union { | |

| __IM uint32_t cm4_scs_nvic_iabr0 | |

| struct { | |

| __IM uint32_t active: 32 | |

| } cm4_scs_nvic_iabr0_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_nvic_iabr1 | |

| struct { | |

| __IM uint32_t active: 32 | |

| } cm4_scs_nvic_iabr1_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_nvic_iabr2 | |

| struct { | |

| __IM uint32_t active: 32 | |

| } cm4_scs_nvic_iabr2_b | |

| }; | |

| __IM uint32_t | RESERVED7 [61] |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr0 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr0_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr1 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr1_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr2 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr2_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr3 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr3_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr4 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr4_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr5 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr5_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr6 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr6_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr7 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr7_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr8 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr8_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr9 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr9_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr10 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr10_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr11 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr11_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr12 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr12_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr13 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr13_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr14 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr14_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr15 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr15_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr16 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr16_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr17 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr17_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr18 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr18_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_nvic_ipr19 | |

| struct { | |

| __IOM uint32_t pri_n0: 8 | |

| __IOM uint32_t pri_n1: 8 | |

| __IOM uint32_t pri_n2: 8 | |

| __IOM uint32_t pri_n3: 8 | |

| } cm4_scs_nvic_ipr19_b | |

| }; | |

| __IM uint32_t | RESERVED8 [556] |

| union { | |

| __IM uint32_t cm4_scs_cpuid | |

| struct { | |

| __IM uint32_t bf_align0: 32 | |

| } cm4_scs_cpuid_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_icsr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_icsr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_vtor | |

| struct { | |

| __IOM uint32_t bf_align0: 7 | |

| __IOM uint32_t tbloff: 25 | |

| } cm4_scs_vtor_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_aircr | |

| struct { | |

| __IOM uint32_t vectreset: 1 | |

| __IOM uint32_t vectclractive: 1 | |

| __IOM uint32_t sysresetreq: 1 | |

| __IOM uint32_t bf_align0: 5 | |

| __IOM uint32_t prigroup: 3 | |

| __IOM uint32_t bf_align1: 4 | |

| __IOM uint32_t endianness: 1 | |

| __IOM uint32_t vectkey: 16 | |

| } cm4_scs_aircr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_scr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_scr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_ccr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_ccr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_shpr1 | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_shpr1_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_shpr2 | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_shpr2_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_shpr3 | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_shpr3_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_shcsr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_shcsr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_cfsr | |

| struct { | |

| __IOM uint32_t mmfsr_iaccviol: 1 | |

| __IOM uint32_t mmfsr_daccviol: 1 | |

| __IOM uint32_t bf_align0: 1 | |

| __IOM uint32_t mmfsr_munstkerr: 1 | |

| __IOM uint32_t mmfsr_mstkerr: 1 | |

| __IOM uint32_t mmfsr_lsperr: 1 | |

| __IOM uint32_t bf_align1: 1 | |

| __IOM uint32_t mmfsr_mmarvalid: 1 | |

| __IOM uint32_t bfsr_ibuserr: 1 | |

| __IOM uint32_t bfsr_preciserr: 1 | |

| __IOM uint32_t bfsr_impreciserr: 1 | |

| __IOM uint32_t bfsr_unstkerr: 1 | |

| __IOM uint32_t bfsr_stkerr: 1 | |

| __IOM uint32_t bfsr_lsperr: 1 | |

| __IOM uint32_t bf_align2: 1 | |

| __IOM uint32_t bfsr_bfarvalid: 1 | |

| __IOM uint32_t ufsr_undefinstr: 1 | |

| __IOM uint32_t ufsr_invstate: 1 | |

| __IOM uint32_t ufsr_invpc: 1 | |

| __IOM uint32_t ufsr_nocp: 1 | |

| __IOM uint32_t bf_align3: 4 | |

| __IOM uint32_t ufsr_unaligned: 1 | |

| __IOM uint32_t ufsr_divbyzero: 1 | |

| __IOM uint32_t bf_align4: 6 | |

| } cm4_scs_cfsr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_hfsr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_hfsr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_dfsr | |

| struct { | |

| __IOM uint32_t halted: 1 | |

| __IOM uint32_t bkpt: 1 | |

| __IOM uint32_t dwttrap: 1 | |

| __IOM uint32_t vcatch: 1 | |

| __IOM uint32_t external: 1 | |

| __IOM uint32_t bf_align0: 27 | |

| } cm4_scs_dfsr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_mmfar | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_mmfar_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_bfar | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_bfar_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_afsr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_afsr_b | |

| }; | |

| __IM uint32_t | RESERVED9 [18] |

| union { | |

| __IOM uint32_t cm4_scs_cpacr | |

| struct { | |

| __IOM uint32_t bf_align0: 32 | |

| } cm4_scs_cpacr_b | |

| }; | |

| __IM uint32_t | RESERVED10 [25] |

| union { | |

| __IOM uint32_t cm4_scs_dhcsr | |

| struct { | |

| __IOM uint32_t c_debugen: 1 | |

| __IOM uint32_t c_halt: 1 | |

| __IOM uint32_t c_step: 1 | |

| __IOM uint32_t c_maskints: 1 | |

| __IOM uint32_t bf_align0: 1 | |

| __IOM uint32_t c_snapstall: 1 | |

| __IOM uint32_t bf_align1: 10 | |

| __IOM uint32_t s_regrdy: 1 | |

| __IOM uint32_t s_halt: 1 | |

| __IOM uint32_t s_sleep: 1 | |

| __IOM uint32_t s_lockup: 1 | |

| __IOM uint32_t bf_align2: 4 | |

| __IOM uint32_t s_retire_st: 1 | |

| __IOM uint32_t s_reset_st: 1 | |

| __IOM uint32_t bf_align3: 6 | |

| } cm4_scs_dhcsr_b | |

| }; | |

| union { | |

| __OM uint32_t cm4_scs_dcrsr | |

| struct { | |

| __OM uint32_t regsel: 7 | |

| __OM uint32_t bf_align0: 9 | |

| __OM uint32_t regwnr: 1 | |

| __OM uint32_t bf_align1: 15 | |

| } cm4_scs_dcrsr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_dcrdr | |

| struct { | |

| __IOM uint32_t dbgtmp: 32 | |

| } cm4_scs_dcrdr_b | |

| }; | |

| union { | |

| __IOM uint32_t cm4_scs_demcr | |

| struct { | |

| __IOM uint32_t vc_corereset: 1 | |

| __IOM uint32_t bf_align0: 3 | |

| __IOM uint32_t vc_mmerr: 1 | |

| __IOM uint32_t vc_nocperr: 1 | |

| __IOM uint32_t vc_chkerr: 1 | |

| __IOM uint32_t vc_staterr: 1 | |

| __IOM uint32_t vc_buserr: 1 | |

| __IOM uint32_t vc_interr: 1 | |

| __IOM uint32_t vc_harderr: 1 | |

| __IOM uint32_t bf_align1: 5 | |

| __IOM uint32_t mon_en: 1 | |

| __IOM uint32_t mon_pend: 1 | |

| __IOM uint32_t mon_step: 1 | |

| __IOM uint32_t mon_req: 1 | |

| __IOM uint32_t bf_align2: 4 | |

| __IOM uint32_t trcena: 1 | |

| __IOM uint32_t bf_align3: 7 | |

| } cm4_scs_demcr_b | |

| }; | |

| __IM uint32_t | RESERVED11 [116] |

| union { | |

| __IM uint32_t cm4_scs_pidr4 | |

| struct { | |

| __IM uint32_t bf_align0: 32 | |

| } cm4_scs_pidr4_b | |

| }; | |

| __IM uint32_t | RESERVED12 [3] |

| union { | |

| __IM uint32_t cm4_scs_pidr0 | |

| struct { | |

| __IM uint32_t bf_align0: 32 | |

| } cm4_scs_pidr0_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_pidr1 | |

| struct { | |

| __IM uint32_t bf_align0: 32 | |

| } cm4_scs_pidr1_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_pidr2 | |

| struct { | |

| __IM uint32_t bf_align0: 32 | |

| } cm4_scs_pidr2_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_pidr3 | |

| struct { | |

| __IM uint32_t bf_align0: 32 | |

| } cm4_scs_pidr3_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_cidr0 | |

| struct { | |

| __IM uint32_t prmbl_0: 8 | |

| __IM uint32_t bf_align0: 24 | |

| } cm4_scs_cidr0_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_cidr1 | |

| struct { | |

| __IM uint32_t prmbl_1: 4 | |

| __IM uint32_t cclass: 4 | |

| __IM uint32_t bf_align0: 24 | |

| } cm4_scs_cidr1_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_cidr2 | |

| struct { | |

| __IM uint32_t prmbl_2: 8 | |

| __IM uint32_t bf_align0: 24 | |

| } cm4_scs_cidr2_b | |

| }; | |

| union { | |

| __IM uint32_t cm4_scs_cidr3 | |

| struct { | |

| __IM uint32_t prmbl_3: 8 | |

| __IM uint32_t bf_align0: 24 | |

| } cm4_scs_cidr3_b | |

| }; | |

cm4_scs (cm4_scs)

Definition at line 224 of file netx90_app.h.

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IM uint32_t cm4_scs_Type::active |

[31..0] For register cm4_scs_nvic_iabr[n], shows whether interrupt (m+(32*n)) is active.

Definition at line 462 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bf_align0 |

[31..0] bitField alignment value for aeabi compatibility

[6..0] bitField alignment value for aeabi compatibility

[7..3] bitField alignment value for aeabi compatibility

[2..2] bitField alignment value for aeabi compatibility

[31..5] bitField alignment value for aeabi compatibility

[4..4] bitField alignment value for aeabi compatibility

[3..1] bitField alignment value for aeabi compatibility

Definition at line 231 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::bf_align0 |

[31..0] bitField alignment value for aeabi compatibility

[31..8] bitField alignment value for aeabi compatibility

Definition at line 264 of file netx90_app.h.

| __OM uint32_t cm4_scs_Type::bf_align0 |

[15..7] bitField alignment value for aeabi compatibility

Definition at line 1115 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bf_align1 |

[14..11] bitField alignment value for aeabi compatibility

[6..6] bitField alignment value for aeabi compatibility

[15..6] bitField alignment value for aeabi compatibility

[15..11] bitField alignment value for aeabi compatibility

Definition at line 861 of file netx90_app.h.

| __OM uint32_t cm4_scs_Type::bf_align1 |

[31..17] bitField alignment value for aeabi compatibility

Definition at line 1118 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bf_align2 |

[14..14] bitField alignment value for aeabi compatibility

[23..20] bitField alignment value for aeabi compatibility

Definition at line 943 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bf_align3 |

[23..20] bitField alignment value for aeabi compatibility

[31..26] bitField alignment value for aeabi compatibility

[31..25] bitField alignment value for aeabi compatibility

Definition at line 953 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bf_align4 |

[31..26] bitField alignment value for aeabi compatibility

Definition at line 959 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bfsr_bfarvalid |

[15..15] BFAR has valid contents.

Definition at line 944 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bfsr_ibuserr |

[8..8] A bus fault on an instruction prefetch has occurred. The fault is signaled only if the instruction is issued.

Definition at line 935 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bfsr_impreciserr |

[10..10] Imprecise data access error has occurred.

Definition at line 939 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bfsr_lsperr |

[13..13] A bus fault occurred during FP lazy state preservation.

Definition at line 942 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bfsr_preciserr |

[9..9] A precise data access error has occurred, and the processor has written the faulting address to the BFAR.

Definition at line 937 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bfsr_stkerr |

[12..12] A derived bus fault has occurred on exception entry.

Definition at line 941 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bfsr_unstkerr |

[11..11] A derived bus fault has occurred on exception return.

Definition at line 940 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::bkpt |

[1..1] Indicates a debug event generated by BKPT instruction execution or a breakpoint match in FPB.

Definition at line 980 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::c_debugen |

[0..0] Halting debug enable bit. If a debugger writes to DHCSR to change the value of this bit from 0 to 1, it must also write 0 to the C_MASKINTS bit, otherwise behavior is UNPREDICTABLE. This bit can only be written by the DAP, it ignores writes from software.

Definition at line 1030 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::c_halt |

[1..1] Processor halt bit. The effects of writes to this bit are: - 0: Causes the processor to leave Debug state, if in Debug state. - 1: Halt the processor. This bit is UNKNOWN after a Power-on reset, and is 0 after a Local reset.

Definition at line 1035 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::c_maskints |

[3..3] When debug is enabled, the debugger can write to this bit to mask PendSV, SysTick and external configurable interrupts:

Definition at line 1042 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::c_snapstall |

[5..5] Allow imprecise entry to Debug state. The actions on writing to this bit are: - 0: No action. - 1: Allow imprecise entry to Debug state, for example by forcing any stalled load or store instruction to complete. Setting this bit to 1 allows a debugger to request imprecise entry to Debug state. The effect of setting this bit to 1 is UNPREDICTABLE unless the DHCSR write also sets C_DEBUGEN and C_HALT to

Definition at line 1052 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::c_step |

[2..2] Processor step bit. The effects of writes to this bit are: - 0: No effect. - 1: Single step enabled. This bit is UNKNOWN after a Power-on reset.

Definition at line 1039 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::cclass |

[7..4] Component class.

Definition at line 1267 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::clrena |

[31..0] For register cm4_scs_nvic_icer[n], disables or shows the current enabled state of interrupt (m+(32*n)): 0: On reads, interrupt disabled. On writes, no effect. 1: On reads, interrupt enabled. On writes, disable interrupt. Software can disable multiple interrupts in a single write to cm4_scs_nvic_icer[n].

Definition at line 317 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::clrpend |

[31..0] For register cm4_scs_nvic_ispr[n], clears the pending state of interrupt (m+(32*n)), or shows whether the state of the interrupt is pending: 0: On reads, interrupt is not pending. On writes, no effect. 1: On reads, interrupt is pending. On writes, clears the pending state of interrupt. Software can clear the pending state of multiple interrupts in a single write to cm4_scs_nvic_icpr[n].

Definition at line 413 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::cm4_scs_actlr |

(@ 0x00000008) Auxiliary control register

Definition at line 228 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_actlr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_afsr |

(@ 0x00000D3C) Auxiliary Fault Status Register

Definition at line 1007 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_afsr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_aircr |

(@ 0x00000D0C) Application interrupt and reset control reister Sets or returns interrupt control data.

Definition at line 838 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_aircr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_bfar |

(@ 0x00000D38) BusFault Address Register

Definition at line 999 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_bfar_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_ccr |

(@ 0x00000D14) Configuration and control Register

Definition at line 880 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_ccr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_cfsr |

(@ 0x00000D28) Configurable Fault Status Register Contains the three Configurable Fault Status Registers.

Definition at line 920 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_cfsr_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_cidr0 |

(@ 0x00000FF0) Component ID Register 0

Definition at line 1254 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_cidr0_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_cidr1 |

(@ 0x00000FF4) Component ID Register 1

Definition at line 1263 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_cidr1_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_cidr2 |

(@ 0x00000FF8) Component ID Register 2

Definition at line 1273 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_cidr2_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_cidr3 |

(@ 0x00000FFC) Component ID Register 3

Definition at line 1282 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_cidr3_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_cpacr |

(@ 0x00000D88) Coprocessor Access Control Register

Definition at line 1016 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_cpacr_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_cpuid |

(@ 0x00000D00) CPUID base register

Definition at line 812 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_cpuid_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_dcrdr |

(@ 0x00000DF8) Debug core register data register With the DCRSR, the DCRDR provides debug access to the ARM core registers, special-purpose registers, and Floating-point extension registers. The DCRDR is the data register for these accesses. Used on its own, the DCRDR provides a message passing resource between an external debugger and a debug agent running on the processor. Note: The architecture does not define any handshaking mechanism for this use of DCRDR.

Definition at line 1123 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_dcrdr_b |

| __OM uint32_t cm4_scs_Type::cm4_scs_dcrsr |

(@ 0x00000DF4) Debug core register selector register With the DCRDR, the DCRSR provides debug access to the ARM core registers, special-purpose registers, and Floating-point extension registers. A write to DCRSR specifies the register to transfer, whether the transfer is a read or a write, and starts the transfer.

Definition at line 1098 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_dcrsr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_demcr |

(@ 0x00000DFC) Debug exception and monitor control register Manages vector catch behavior and DebugMonitor handling when debugging.

Definition at line 1143 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_demcr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_dfsr |

(@ 0x00000D30) Debug fault status Register Shows which debug event occurred. Note: Writing 1 to a register bit clears the bit to 0.

Definition at line 972 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_dfsr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_dhcsr |

(@ 0x00000DF0) Debug halting control and status register Controls halting debug. Note: On writes bits 31-16 (dbgkey) must be set to 0xA05F.

Definition at line 1025 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_dhcsr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_hfsr |

(@ 0x00000D2C) HardFault Status Register

Definition at line 964 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_hfsr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_icsr |

(@ 0x00000D04) Interrupt control and state register

Definition at line 820 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_icsr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_mmfar |

(@ 0x00000D34) MemManage Faul Address Register

Definition at line 991 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_mmfar_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_nvic_iabr0 |

(@ 0x00000300) Interrupt active bit register 0 For a group of 32 interrupts, shows whether each interrupt is active.

Definition at line 457 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_iabr0_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_nvic_iabr1 |

(@ 0x00000304) Interrupt active bit register 1 For a group of 32 interrupts, shows whether each interrupt is active.

Definition at line 468 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_iabr1_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_nvic_iabr2 |

(@ 0x00000308) Interrupt active bit register 2 For a group of 32 interrupts, shows whether each interrupt is active.

Definition at line 479 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_iabr2_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_icer0 |

(@ 0x00000180) Interrupt clear-enable register 0 Disables, or reads the enable state of a group of interrupts.

Definition at line 313 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_icer0_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_icer1 |

(@ 0x00000184) Interrupt clear-enable register 1 Disables, or reads the enable state of a group of interrupts.

Definition at line 327 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_icer1_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_icer2 |

(@ 0x00000188) Interrupt clear-enable register 2 Disables, or reads the enable state of a group of interrupts.

Definition at line 341 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_icer2_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_icpr0 |

(@ 0x00000280) Interrupt clear-pending register 0 For a group of interrupts, clears the interrupt pending status, or shows the current pending status.

Definition at line 408 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_icpr0_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_icpr1 |

(@ 0x00000284) Interrupt clear-pending register 1 For a group of interrupts, clears the interrupt pending status, or shows the current pending status.

Definition at line 424 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_icpr1_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_icpr2 |

(@ 0x00000288) Interrupt clear-pending register 2 For a group of interrupts, clears the interrupt pending status, or shows the current pending status.

Definition at line 440 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_icpr2_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr0 |

(@ 0x00000400) Interrupt priority register 0 Sets or reads interrupt priorities.

Definition at line 491 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr0_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr1 |

(@ 0x00000404) Interrupt priority register 1 Sets or reads interrupt priorities.

Definition at line 507 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr10 |

(@ 0x00000428) Interrupt priority register 10 Sets or reads interrupt priorities.

Definition at line 651 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr10_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr11 |

(@ 0x0000042C) Interrupt priority register 11 Sets or reads interrupt priorities.

Definition at line 667 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr11_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr12 |

(@ 0x00000430) Interrupt priority register 12 Sets or reads interrupt priorities.

Definition at line 683 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr12_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr13 |

(@ 0x00000434) Interrupt priority register 13 Sets or reads interrupt priorities.

Definition at line 699 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr13_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr14 |

(@ 0x00000438) Interrupt priority register 14 Sets or reads interrupt priorities.

Definition at line 715 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr14_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr15 |

(@ 0x0000043C) Interrupt priority register 15 Sets or reads interrupt priorities.

Definition at line 731 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr15_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr16 |

(@ 0x00000440) Interrupt priority register 16 Sets or reads interrupt priorities.

Definition at line 747 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr16_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr17 |

(@ 0x00000444) Interrupt priority register 17 Sets or reads interrupt priorities.

Definition at line 763 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr17_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr18 |

(@ 0x00000448) Interrupt priority register 18 Sets or reads interrupt priorities.

Definition at line 779 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr18_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr19 |

(@ 0x0000044C) Interrupt priority register 19 Sets or reads interrupt priorities.

Definition at line 795 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr19_b |

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr1_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr2 |

(@ 0x00000408) Interrupt priority register 2 Sets or reads interrupt priorities.

Definition at line 523 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr2_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr3 |

(@ 0x0000040C) Interrupt priority register 3 Sets or reads interrupt priorities.

Definition at line 539 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr3_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr4 |

(@ 0x00000410) Interrupt priority register 4 Sets or reads interrupt priorities.

Definition at line 555 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr4_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr5 |

(@ 0x00000414) Interrupt priority register 5 Sets or reads interrupt priorities.

Definition at line 571 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr5_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr6 |

(@ 0x00000418) Interrupt priority register 6 Sets or reads interrupt priorities.

Definition at line 587 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr6_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr7 |

(@ 0x0000041C) Interrupt priority register 7 Sets or reads interrupt priorities.

Definition at line 603 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr7_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr8 |

(@ 0x00000420) Interrupt priority register 8 Sets or reads interrupt priorities.

Definition at line 619 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr8_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ipr9 |

(@ 0x00000424) Interrupt priority register 9 Sets or reads interrupt priorities.

Definition at line 635 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ipr9_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_iser0 |

(@ 0x00000100) Interrupt set-enable register 0 Enables, or reads the enable state of a group of interrupts.

Definition at line 270 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_iser0_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_iser1 |

(@ 0x00000104) Interrupt set-enable register 1 Enables, or reads the enable state of a group of interrupts.

Definition at line 284 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_iser1_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_iser2 |

(@ 0x00000108) Interrupt set-enable register 2 Enables, or reads the enable state of a group of interrupts.

Definition at line 298 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_iser2_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ispr0 |

(@ 0x00000200) Interrupt set-pending register 0 For a group of interrupts, changes interrupt status to pending, or shows the current pending status.

Definition at line 356 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ispr0_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ispr1 |

(@ 0x00000204) Interrupt set-pending register 1 For a group of interrupts, changes interrupt status to pending, or shows the current pending status.

Definition at line 373 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ispr1_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_nvic_ispr2 |

(@ 0x00000208) Interrupt set-pending register 2 For a group of interrupts, changes interrupt status to pending, or shows the current pending status.

Definition at line 390 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_nvic_ispr2_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_pidr0 |

(@ 0x00000FE0) Peripheral ID Register 0

Definition at line 1222 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_pidr0_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_pidr1 |

(@ 0x00000FE4) Peripheral ID Register 1

Definition at line 1230 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_pidr1_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_pidr2 |

(@ 0x00000FE8) Peripheral ID Register 2

Definition at line 1238 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_pidr2_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_pidr3 |

(@ 0x00000FEC) Peripheral ID Register 3

Definition at line 1246 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_pidr3_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_pidr4 |

(@ 0x00000FD0) Peripheral ID Register 4

Definition at line 1213 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_pidr4_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_scr |

(@ 0x00000D10) System control Register

Definition at line 872 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_scr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_shcsr |

(@ 0x00000D24) System Handler Control and State Register

Definition at line 912 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_shcsr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_shpr1 |

(@ 0x00000D18) System Handler Priority Register 1

Definition at line 888 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_shpr1_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_shpr2 |

(@ 0x00000D1C) System Handler Priority Register 2

Definition at line 896 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_shpr2_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_shpr3 |

(@ 0x00000D20) System Handler Priority Register 3

Definition at line 904 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_shpr3_b |

| __IM uint32_t cm4_scs_Type::cm4_scs_stcr |

(@ 0x0000001C) SysTick calibration value register

Definition at line 261 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_stcr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_stcsr |

(@ 0x00000010) SysTick control and status register

Definition at line 237 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_stcsr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_stcvr |

(@ 0x00000018) SysTick current value register

Definition at line 253 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_stcvr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_strvr |

(@ 0x00000014) SysTick Reload Value register

Definition at line 245 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_strvr_b |

| __IOM uint32_t cm4_scs_Type::cm4_scs_vtor |

(@ 0x00000D08) Vector table offset register Holds the vector table address.

Definition at line 828 of file netx90_app.h.

| struct { ... } cm4_scs_Type::cm4_scs_vtor_b |

| __IOM uint32_t cm4_scs_Type::dbgtmp |

[31..0] Data temporary cache, for reading and writing the ARM core registers, special-purpose registers, and Floating-point extension registers.

Definition at line 1136 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::dwttrap |

[2..2] Indicates a debug event generated by the DWT.

Definition at line 982 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::endianness |

[15..15] Indicates the memory system endianness: 0 - Little endian, 1 - Big endian. This bit is static or configured by a hardware input on reset. This bit is read only.

Definition at line 862 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::external |

[4..4] Indicates a debug event generated because of the assertion of an external debug request.

Definition at line 984 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::halted |

[0..0] Indicates a debug event generated by either: - A C_HALT or C_STEP request, triggered by a write to the DHCSR. - A step request triggered by setting DEMCR.MON_STEP to 1.

Definition at line 977 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mmfsr_daccviol |

[1..1] Data access violation. The MMFAR shows the data address that the load or store tried to access.

Definition at line 927 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mmfsr_iaccviol |

[0..0] MPU or Execute Never (XN) default memory map access violation on an instruction fetch has occurred. The fault is signalled only if the instruction is issued.

Definition at line 924 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mmfsr_lsperr |

[5..5] A MemManage fault occurred during FP lazy state preservation.

Definition at line 932 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mmfsr_mmarvalid |

[7..7] MMFAR has valid contents.

Definition at line 934 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mmfsr_mstkerr |

[4..4] A derived MemManage fault occurred on exception entry.

Definition at line 931 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mmfsr_munstkerr |

[3..3] A derived MemManage fault occurred on exception return.

Definition at line 930 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mon_en |

[16..16] Enable the DebugMonitor exception. If DHCSR.C_DEBUGEN is set to 1, the processor ignores the value of this bit.

Definition at line 1176 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mon_pend |

[17..17] Sets or clears the pending state of the DebugMonitor exception: - 0: Clear the status of the DebugMonitor exception to not pending. - 1: Set the status of the DebugMonitor exception to pending. When the DebugMonitor exception is pending it becomes active subject to the exception priority rules. A debugger can use this bit to wakeup the monitor using the DAP. The effect of setting this bit to 1 is not affected by the value of the MON_EN bit. A debugger can set MON_PEND to 1, and force the processor to take

Definition at line 1178 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mon_req |

[19..19] DebugMonitor semaphore bit. The processor does not use this bit. The monitor software defines the meaning and use of this bit.

Definition at line 1194 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::mon_step |

[18..18] When MON_EN is set to 0, this feature is disabled and the processor ignores MON_STEP. When MON_EN is set to 1, the meaning of MON_STEP is: - 0: Do not step the processor.

Definition at line 1187 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::pri_n0 |

[7..0] For register cm4_scs_nvic_ipr[n], priority of interrupt number 4n.

Definition at line 495 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::pri_n1 |

[15..8] For register cm4_scs_nvic_ipr[n], priority of interrupt number 4n+1.

Definition at line 497 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::pri_n2 |

[23..16] For register cm4_scs_nvic_ipr[n], priority of interrupt number 4n+2.

Definition at line 499 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::pri_n3 |

[31..24] For register cm4_scs_nvic_ipr[n], priority of interrupt number 4n+3.

Definition at line 501 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::prigroup |

[10..8] Priority grouping, indicates the binary point position.

Definition at line 860 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::prmbl_0 |

[7..0] Preamble byte 0.

Definition at line 1257 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::prmbl_1 |

[3..0] Preamble bits[11:8].

Definition at line 1266 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::prmbl_2 |

[7..0] Preamble byte 2.

Definition at line 1276 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::prmbl_3 |

[7..0] Preamble byte 3.

Definition at line 1285 of file netx90_app.h.

| __OM uint32_t cm4_scs_Type::regsel |

[6..0] Specifies the ARM core register, special-purpose register, or Floating-point extension register, to transfer: { | 0 - 12 ARM core registers R0-R12. 13 The current SP. See also values 17 (MSP) and 18 (PSP). 14 LR. 15 DebugReturnAddress. 16 xPSR. 17 Main stack pointer, MSP. 18 Process stack pointer, PSP. 20 Bits[31:24]: CONTROL, Bits[23:16]: FAULTMASK, Bits[15:8]: BASEPRI, Bits[7:0]: PRIMASK. In each field, the valid bits are packed with leading zeros. For example, FAULTMASK i

Definition at line 1107 of file netx90_app.h.

| __OM uint32_t cm4_scs_Type::regwnr |

[16..16] Specifies the access type for the transfer: 0 : Read. 1 : Write.

Definition at line 1116 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED[2] |

< (@ 0xE000E000) cm4_scs Structure

Definition at line 225 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED1 |

Definition at line 234 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED10[25] |

Definition at line 1022 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED11[116] |

Definition at line 1210 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED12[3] |

Definition at line 1219 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED2[56] |

Definition at line 267 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED3[29] |

Definition at line 310 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED4[29] |

Definition at line 353 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED5[29] |

Definition at line 405 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED6[29] |

Definition at line 454 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED7[61] |

Definition at line 488 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED8[556] |

Definition at line 809 of file netx90_app.h.

| __IM uint32_t cm4_scs_Type::RESERVED9[18] |

Definition at line 1013 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::s_halt |

[17..17] Indicates whether the processor is in Debug state. This bit is read-only.

Definition at line 1069 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::s_lockup |

[19..19] Indicates whether the processor is locked up because of an unrecoverable exception. This bit can only be read as 1 by a remote debugger, using the DAP. The value of 1 indicates that the processor is running but locked up. The bit clears to 0 when the processor enters Debug state. This bit is read-only.

Definition at line 1075 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::s_regrdy |

[16..16] A handshake flag for transfers through the DCRDR: - Writing to DCRSR clears the bit to 0. - Completion of the DCRDR transfer then sets the bit to 1. For more information about DCRDR transfers see Debug Core Register Data Register, DCRDR. This bit is valid only when the processor is in Debug state, otherwise the bit is UNKNOWN. This bit is read-only.

Definition at line 1062 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::s_reset_st |

[25..25] Indicates whether the processor has been reset since the last read of DHCSR. This is a sticky bit, that clears to 0 on a read of DHCSR. This bit is read-only.

Definition at line 1090 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::s_retire_st |

[24..24] Set to 1 every time the processor retires one or more instructions. This is a sticky bit, that clears to 0 on a read of DHCSR. The architecture does not define precisely when this bit is set to 1. It requires only that this happen periodically in Non-debug state to indicate that software execution is progressing. This bit is UNKNOWN after a Power-on or Local reset, but then is set to 1 as soon as the processor executes and retires an instruction. This bit is read-only.

Definition at line 1082 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::s_sleep |

[18..18] Indicates whether the processor is sleeping. The debugger must set the C_HALT bit to 1 to gain control, or wait for an interrupt or other wakeup event to wakeup the system. This bit is read-only.

Definition at line 1071 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::setena |

[31..0] For register cm4_scs_nvic_iser[n], enables or shows the current enabled state of interrupt (m+(32*n)): 0: On reads, interrupt disabled. On writes, no effect. 1: On reads, interrupt enabled. On writes, enable interrupt. Software can enable multiple interrupts in a single write to cm4_scs_nvic_iser[n].

Definition at line 274 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::setpend |

[31..0] For register cm4_scs_nvic_ispr[n], changes the state of interrupt (m+(32*n)) to pending, or shows whether the state of the interrupt is pending: 0: On reads, interrupt is not pending. On writes, no effect. 1: On reads, interrupt is pending. On writes, change state of interrupt to pending. Software can set multiple interrupts to pending state in a single write to cm4_scs_nvic_ispr[n].

Definition at line 362 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::sysresetreq |

[2..2] System Reset Request. Writing 1 to this bit asserts a signal to the external system to request a Local reset. A Local or Power-on reset clears this bit to 0.

Definition at line 856 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::tbloff |

[31..7] Bits[31:7] of the vector table address.

Definition at line 833 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::trcena |

[24..24] Global enable for all DWT and ITM features: - 0: DWT and ITM units disabled. - 1: DWT and ITM units enabled. If the DWT and ITM units are not implemented, this bit is UNK/SBZP. When TRCENA is set to 0: - DWT registers return UNKNOWN values on reads. Whether the processor ignores writes to the DWT unit is IMPLEMENTATION DEFINED. - ITM registers return UNKNOWN values on reads. Whether the processor ignores writes to the ITM unit is IMPLEMENTATION DEFINED. Setting this bit to 0 might not stop all events. To e

Definition at line 1198 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::ufsr_divbyzero |

[25..25] Divide by zero error has occurred.

Definition at line 958 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::ufsr_invpc |

[18..18] An integrity check error has occurred on EXC_RETURN.

Definition at line 950 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::ufsr_invstate |

[17..17] Instruction executed with invalid EPSR.T or EPSR.IT field.

Definition at line 948 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::ufsr_nocp |

[19..19] A coprocessor access error has occurred. This shows that the coprocessor is disabled or not present.

Definition at line 951 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::ufsr_unaligned |

[24..24] Unaligned access error has occurred. Multi-word accesses always fault if not word aligned. Software can configure unaligned word and halfword accesses to fault, by enabling UNALIGN_TRP in the CCR.

Definition at line 954 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::ufsr_undefinstr |

[16..16] The processor has attempted to execute an undefined instruction. This might be an undefined instruction associated with an enabled coprocessor.

Definition at line 945 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vc_buserr |

[8..8] Enable halting debug trap on a BusFault exception. If DHCSR.C_DEBUGEN is set to 0, the processor ignores the value of this bit.

Definition at line 1166 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vc_chkerr |

[6..6] Enable halting debug trap on a UsageFault exception caused by a checking error, for example an alignment check error. If DHCSR.C_DEBUGEN is set to 0, the processor ignores the value of this bit.

Definition at line 1158 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vc_corereset |

[0..0] Enable Reset Vector Catch. This causes a Local reset to halt a running system. If DHCSR.C_DEBUGEN is set to 0, the processor ignores the value of this bit.

Definition at line 1148 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vc_harderr |

[10..10] Enable halting debug trap on a HardFault exception. If DHCSR.C_DEBUGEN is set to 0, the processor ignores the value of this bit.

Definition at line 1172 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vc_interr |

[9..9] Enable halting debug trap on a fault occurring during exception entry or exception return. If DHCSR.C_DEBUGEN is set to 0, the processor ignores the value of this bit.

Definition at line 1169 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vc_mmerr |

[4..4] Enable halting debug trap on a MemManage exception. If DHCSR.C_DEBUGEN is set to 0, the processor ignores the value of this bit.

Definition at line 1152 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vc_nocperr |

[5..5] Enable halting debug trap on a UsageFault caused by an access to a Coprocessor. If DHCSR.C_DEBUGEN is set to 0, the processor ignores the value of this bit.

Definition at line 1155 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vc_staterr |

[7..7] Enable halting debug trap on a UsageFault exception caused by a state information error, for example an Undefined Instruction exception. If DHCSR.C_DEBUGEN is set to 0, the processor ignores the value of this bit.

Definition at line 1162 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vcatch |

[3..3] Indicates triggering of a Vector catch.

Definition at line 983 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vectclractive |

[1..1] Writing 1 to this bit clears all active state information for fixed and configurable exceptions. This includes clearing the IPSR to zero. The effect of writing a 1 to this bit if the processor is not halted in Debug state is UNPREDICTABLE. This bit is write only.

Definition at line 851 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vectkey |

[31..16] Vector Key. Register writes must write 0x05FA to this field, otherwise the write is ignored. On reads, returns 0xFA05.

Definition at line 865 of file netx90_app.h.

| __IOM uint32_t cm4_scs_Type::vectreset |

[0..0] Writing 1 to this bit causes a local system reset. This bit self-clears. The effect of writing a 1 to this bit if the processor is not halted in Debug state is UNPREDICTABLE. When the processor is halted in Debug state, if a write to the register writes a 1 to both VECTRESET and SYSRESETREQ, the behavior is UNPREDICTABLE. This bit is write only. Note: The netx90 doesn't support a local system reset. Writing 1 results in UNPREDICTABLE behaviour of the whole system! Use sysresetreq instead!

Definition at line 842 of file netx90_app.h.