|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

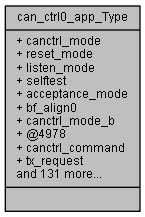

can_ctrl0_app (can_ctrl0_app) More...

#include <netx90_app.h>

can_ctrl0_app (can_ctrl0_app)

Definition at line 23386 of file netx90_app.h.

| union { ... } |

< (@ 0xFF801200) can_ctrl0_app Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __OM uint32_t can_ctrl0_app_Type::abort_tx |

[1..1] Abort Transmission, self-clearing 1 present; if not already in progress, a pending transmission request is cancelled Setting the command bits tx_request and abort_tx simultaneously results in sending the transmit message once. No re-transmission will be performed in the event of an error or arbitration lost (single-shot transmission).

Definition at line 23422 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::acceptance_mode |

[3..3] Acceptance Filter Mode 1 single; the single acceptance filter option is enabled (one filter with the length of 32 bit is active) 0 dual; the dual acceptance filter option is enabled (two filters, each with the length of 16 bit are active)

Definition at line 23407 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::arb_lost_irq |

[6..6] Arbitration Lost Interrupt 1 set; this bit is set when the CAN controller lost the arbitration and becomes a receiver and the arb_lost_irq_en bit is set within the interrupt enable register, will only get active again if canctrl_arb_lost_capture register is read 0 reset

Definition at line 23504 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::arb_lost_irq_en |

[6..6] Arbitration Lost Interrupt Enable 1 enabled; if the CAN controller has lost arbitration, the respective interrupt is requested 0 disabled

Definition at line 23543 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::bf_align0 |

[31..4] bitField alignment value for aeabi compatibility

[4..4] bitField alignment value for aeabi compatibility

[31..0] bitField alignment value for aeabi compatibility

[31..11] bitField alignment value for aeabi compatibility

[6..6] bitField alignment value for aeabi compatibility

[31..8] bitField alignment value for aeabi compatibility

Definition at line 23412 of file netx90_app.h.

| __OM uint32_t can_ctrl0_app_Type::bf_align0 |

[31..5] bitField alignment value for aeabi compatibility

Definition at line 23438 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::bf_align0 |

[31..9] bitField alignment value for aeabi compatibility

[4..4] bitField alignment value for aeabi compatibility

[31..5] bitField alignment value for aeabi compatibility

[31..8] bitField alignment value for aeabi compatibility

[31..7] bitField alignment value for aeabi compatibility

[6..0] bitField alignment value for aeabi compatibility

Definition at line 23472 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::bf_align1 |

[31..8] bitField alignment value for aeabi compatibility

Definition at line 23514 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::bf_align1 |

[31..8] bitField alignment value for aeabi compatibility

[31..13] bitField alignment value for aeabi compatibility

Definition at line 23549 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::bus_error_irq |

[7..7] Bus Error Interrupt 1 set; this bit is set when the CAN controller detects an error on the CAN-bus and the bus_error_irq_en bit is set within the interrupt enable register, will only get active again if canctrl_err_code_capture register is read 0 reset

Definition at line 23509 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::bus_error_irq_en |

[7..7] Bus Error Interrupt Enable 1 enabled; if an bus error has been detected, the CAN controller requests the respective interrupt 0 disabled

Definition at line 23546 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::bus_status |

[7..7] Bus Status 1 bus-off; the CAN controller is not involved in bus activities 0 bus-on; the CAN controller is involved in bus activities

Definition at line 23467 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::canctrl_arb_lost_capture |

(@ 0x0000002C) CAN arbitration lost capture register This register contains information about the bit position of losing arbitration. reading the register will clear all bits in not extended mode: data1

Definition at line 23613 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_arb_lost_capture_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_bus_timing0 |

(@ 0x00000018) CAN bus timing register 0, only writable in reset mode in not extended mode: acceptance_mask_0

Definition at line 23562 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_bus_timing0_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_bus_timing1 |

(@ 0x0000001C) CAN bus timing register 1, only writable in reset mode

Definition at line 23582 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_bus_timing1_b |

| __OM uint32_t can_ctrl0_app_Type::canctrl_command |

(@ 0x00000004) CAN command register

Definition at line 23417 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_command_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data0 |

(@ 0x00000040) CAN data register 0 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: Read or write acceptance code 0 Operating mode: R: Standard frame: Read RX frame information Extended frame: Read RX frame information W: Standard frame: Write TX frame information Extended frame: Write TX frame information } in not extended mode: data6

Definition at line 23705 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data0_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data1 |

(@ 0x00000044) CAN data register 1 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: Read or write acceptance code 1 Operating mode: R: Standard frame: Read RX identifier 1 Extended frame: Read RX identifier 1 W: Standard frame: Write TX identifier 1 Extended frame: Write TX identifier 1 } in not extended mode: data7

Definition at line 23722 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data10 |

(@ 0x00000068) CAN data register 10 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: reserved Operating mode: R: Standard frame: Read RX data 8 Extended frame: Read RX data 6 W: Standard frame: Write TX data 8 Extended frame: Write TX data 6 }

Definition at line 23867 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data10_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data11 |

(@ 0x0000006C) CAN data register 11 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: reserved Operating mode: R: Standard frame: reserved Extended frame: Read RX data 7 W: Standard frame: reserved Extended frame: Write TX data 7 }

Definition at line 23882 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data11_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data12 |

(@ 0x00000070) CAN data register 12 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: reserved Operating mode: R: Standard frame: reserved Extended frame: Read RX data 8 W: Standard frame: reserved Extended frame: Write TX data 8 }

Definition at line 23897 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data12_b |

| struct { ... } can_ctrl0_app_Type::canctrl_data1_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data2 |

(@ 0x00000048) CAN data register 2 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: Read or write acceptance code 2 Operating mode: R: Standard frame: Read RX identifier 2 Extended frame: Read RX identifier 2 W: Standard frame: Write TX identifier 2 Extended frame: Write TX identifier 2 } in not extended mode: data8

Definition at line 23739 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data2_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data3 |

(@ 0x0000004C) CAN data register 3 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: Read or write acceptance code 3 Operating mode: R: Standard frame: Read RX data 1 Extended frame: Read RX identifier 3 W: Standard frame: Write TX data 1 Extended frame: Write TX identifier 3 } in not extended mode: data9

Definition at line 23756 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data3_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data4 |

(@ 0x00000050) CAN data register 4 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: Read or write acceptance mask 0 Operating mode: R: Standard frame: Read RX data 2 Extended frame: Read RX identifier 4 W: Standard frame: Write TX data 2 Extended frame: Write TX identifier 4 }

Definition at line 23773 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data4_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data5 |

(@ 0x00000054) CAN data register 5 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: Read or write acceptance mask 1 Operating mode: R: Standard frame: Read RX data 3 Extended frame: Read RX data 1 W: Standard frame: Write TX data 3 Extended frame: Write TX data 1 }

Definition at line 23789 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data5_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data6 |

(@ 0x00000058) CAN data register 6 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: Read or write acceptance mask 2 Operating mode: R: Standard frame: Read RX data 4 Extended frame: Read RX data 2 W: Standard frame: Write TX data 4 Extended frame: Write TX data 2 }

Definition at line 23805 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data6_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data7 |

(@ 0x0000005C) CAN data register 7 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: Read or write acceptance mask 3 Operating mode: R: Standard frame: Read RX data 5 Extended frame: Read RX data 3 W: Standard frame: Write TX data 5 Extended frame: Write TX data 3 }

Definition at line 23821 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data7_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data8 |

(@ 0x00000060) CAN data register 8 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: reserved Operating mode: R: Standard frame: Read RX data 6 Extended frame: Read RX data 4 W: Standard frame: Write TX data 6 Extended frame: Write TX data 4 }

Definition at line 23837 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data8_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_data9 |

(@ 0x00000064) CAN data register 9 This register has multiple functions depending on reset mode and read or write access. { | | Reset mode: R/W: reserved Operating mode: R: Standard frame: Read RX data 7 Extended frame: Read RX data 5 W: Standard frame: Write TX data 7 Extended frame: Write TX data 5 }

Definition at line 23852 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_data9_b |

| __IM uint32_t can_ctrl0_app_Type::canctrl_err_code_capture |

(@ 0x00000030) CAN error code capture register This register contains information about the type and location of errors on the bus. reading the register will clear all bits in not extended mode: data2

Definition at line 23633 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_err_code_capture_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_err_warning_limit |

(@ 0x00000034) CAN error warning limit register, only writable in reset mode in not extended mode: data3

Definition at line 23655 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_err_warning_limit_b |

| __IM uint32_t can_ctrl0_app_Type::canctrl_irq |

(@ 0x0000000C) CAN interrupt register reading the register will clear all bits except rx_irq

Definition at line 23477 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_irq_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_irq_en |

(@ 0x00000010) CAN interrupt enable register in not extended mode: acceptance_code_0

Definition at line 23519 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_irq_en_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_mode |

(@ 0x00000000) CAN mode register

Definition at line 23389 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_mode_b |

| __IM uint32_t can_ctrl0_app_Type::canctrl_mode_control |

(@ 0x0000007C) CAN mode control register, only writable in reset mode

Definition at line 23927 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_mode_control_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_not_extended_acceptance_mask0 |

(@ 0x00000014) CAN not extended acceptance mask register

Definition at line 23554 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_not_extended_acceptance_mask0_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_not_extended_data0 |

(@ 0x00000028) CAN not extended data register

Definition at line 23605 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_not_extended_data0_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_rx_error_cnt |

(@ 0x00000038) CAN RX error counter register, only writable in reset mode The RX error counter register reflects the current value of the receive error counter. If a bus-off event occurs, the RX error counter is initialized to logic 0. The time bus-off is valid, writing to this register has no effect. Note, that a CPU-forced content change of the RX error counter is only possible, if the reset mode was entered previously. An error status change (see status register), an error warning or an error passive in

Definition at line 23665 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_rx_error_cnt_b |

| __IM uint32_t can_ctrl0_app_Type::canctrl_rx_message_cnt |

(@ 0x00000074) CAN RX message counter register Reflects the number of messages available within the RXFIFO. The value is incremented with each receive event and decremented by the release receive buffer command. After any reset event, this register is cleared.

Definition at line 23912 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_rx_message_cnt_b |

| __IM uint32_t can_ctrl0_app_Type::canctrl_status |

(@ 0x00000008) CAN status register

Definition at line 23443 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_status_b |

| __IOM uint32_t can_ctrl0_app_Type::canctrl_tx_error_cnt |

(@ 0x0000003C) CAN TX error counter register, only writable in reset mode The TX error counter register reflects the current value of the transmit error counter. If a bus-off event occurs, the TX error counter is initialized to 127 to count the minimum protocol-defined time (128 occurrences of the bus-free signal). Reading the TX error counter during this time gives information about the status of the bus-off recovery. If bus-off is active, a write access to TXERR in the range from 0 to 254 clears the bus-

Definition at line 23685 of file netx90_app.h.

| struct { ... } can_ctrl0_app_Type::canctrl_tx_error_cnt_b |

| __OM uint32_t can_ctrl0_app_Type::clr_overrun |

[3..3] Clear Data Overrun, self-clearing 1 clear; the data overrun status bit is cleared, shall be used together with release_rx_buf to release invalid buffer

Definition at line 23431 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::data |

[7..0] register content (rx data, tx data or acceptance code)

[7..0] register content (rx data, tx data or acceptance mask)

[7..0] register content (rx data or tx data)

Definition at line 23716 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::direction |

[5..5] Direction 1 RX; error occurred during reception 0 TX; error occurred during transmission

Definition at line 23646 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::err_code |

[7..6] Error code { | Binary value Code 00 bit error 01 form error 10 stuff error 11 other type of error }

Definition at line 23648 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::err_passive_irq |

[5..5] Error Passive Interrupt 1 set; this bit is set whenever the CAN controller has reached the error passive status (at least one error counter exceeds the protocol-defined level of 127) or if the CAN controller is in the error passive status and enters the error active status again and the err_passive_irq_en bit is set within the interrupt enable register 0 reset

Definition at line 23497 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::err_passive_irq_en |

[5..5] Error Passive Interrupt Enable 1 enabled; if the error status of the CAN controller changes from error active to error passive or vice versa, the respective interrupt is requested 0 disabled

Definition at line 23539 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::error_status |

[6..6] Error Status 1 error; at least one of the error counters has reached or exceeded the CPU warning limit defined by the Error Warning Limit Register (EWLR) 0 ok; both error counters are below the warning limit

Definition at line 23463 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::limit |

[7..0] error warning limit

Definition at line 23659 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::listen_mode |

[1..1] Listen Only Mode 1 listen only; in this mode the CAN controller would give no acknowledge to the CAN-bus, even if a message is received successfully; the error counters are stopped at the current value 0 normal

Definition at line 23397 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::mode |

[7..7] 0: BasicCAN mode, 1: PeliCAN mode recommended value is 1 (PeliCAN mode), The here given register map of all registers of the CAN controller is valid for PeliCAN only.

Definition at line 23932 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::overrun |

[1..1] Data Overrun Status 1 overrun; a message was lost because there was not enough space for that message in the RXFIFO 0 absent; no data overrun has occurred since the last clear data overrun command was given

Definition at line 23448 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::overrun_irq |

[3..3] Data Overrun Interrup 1 set; this bit is set on a `0-to-1' transition of the data overrun status bit and the overrun_irq_en bit is set within the interrupt enable register 0 reset

Definition at line 23493 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::overrun_irq_en |

[3..3] Data Overrun Interrupt Enable 1 enabled; if the data overrun status bit is set (see status register; Table 14), the CAN controller requests the respective interrupt 0 disabled

Definition at line 23534 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::oversampling |

[7..7] Sampling 1 triple; the bus is sampled three times; recommended for low/medium speed buses (class A and B) where filtering spikes on the bus line is beneficial 0 single; the bus is sampled once; recommended for high speed buses (SAE class C)

Definition at line 23591 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::position |

[4..0] Positon where arbitration was lost { | Decimal value Position 00 arbitration lost in bit 1 of identifier 01 arbitration lost in bit 2 of identifier 02 arbitration lost in bit 3 of identifier 03 arbitration lost in bit 4 of identifier 04 arbitration lost in bit 5 of identifier 05 arbitration lost in bit 6 of identifier 06 arbitration lost in bit 7 of identifier 07 arbitration lost in bit 8 of identifier 08 arbitration lo

Definition at line 23620 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::prescaler |

[8..0] Baud Rate Prescaler The period of the CAN system clock tscl is programmable and determines the individual bit timing. The CAN system clock is calculated using the following equation: tscl = tCLK * prescaler with tCLK = 10 ns

Definition at line 23566 of file netx90_app.h.

| __OM uint32_t can_ctrl0_app_Type::release_rx_buf |

[2..2] Release Receive Buffer, self-clearing 1 released; the receive buffer, representing the message memory space in the RXFIFO is released

Definition at line 23428 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::RESERVED[2] |

Definition at line 23602 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::RESERVED1 |

Definition at line 23924 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::reset_mode |

[0..0] Reset Mode 1 reset; detection of a set reset mode bit results in aborting the current transmission/reception of a message and entering the reset mode 0 normal; on the `1-to-0' transition of the reset mode bit, the CAN controller returns to the operating mode

Definition at line 23392 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::rx_buf_status |

[0..0] Receive Buffer Status 1 full; one or more complete messages are available in the RXFIFO 0 empty; no message is available

Definition at line 23446 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::rx_err |

[7..0] rx error counter

Definition at line 23679 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::rx_irq |

[0..0] Receive Interrupt 1 set; this bit is set while the receive FIFO is not empty and the rx_irq_en bit is set within the interrupt enable register 0 reset; no more message is available within the RXFIFO

Definition at line 23481 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::rx_irq_en |

[0..0] Receive Interrupt Enable 1 enabled; when the receive buffer status is `full' the CAN controller requests the respective interrupt 0 disabled

Definition at line 23523 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::rx_msg_cnt |

[6..0] rx message counter

Definition at line 23920 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::rx_status |

[4..4] Receive Status 1 receive; the CAN controller is receiving a message 0 idle

Definition at line 23459 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::segment |

[4..0] Frame segment where error was detected { | Binary value Segment 00011 start of frame 00010 ID.28 to ID.21 00110 ID.20 to ID.18 00100 bit SRTR 00101 bit IDE 00111 ID.17 to ID.13 01111 ID.12 to ID.5 01110 ID.4 to ID.0 01100 bit RTR 01101 reser ved bit 1 01001 reser ved bit 0 01011 data length code 01010 data field 01000 CRC sequence 11000

Definition at line 23640 of file netx90_app.h.

| __OM uint32_t can_ctrl0_app_Type::self_rx_request |

[4..4] Self Reception Request, self-clearing 1 present; a message shall be transmitted and received simultaneously Setting tx_request and self_rx_request simultaneously will ignore the set self_rx_request bit.

Definition at line 23434 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::selftest |

[2..2] Self Test Mode 1 self test; in this mode a full node test is possible without any other active node on the bus using the self reception request command; the CAN controller will perform a successful transmission, even if there is no acknowledge received 0 normal; an acknowledge is required for successful transmission

Definition at line 23401 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::sync_jump_width |

[10..9] Synchronization Jump Width To compensate for phase shifts between clock oscillators of different bus controllers, any bus controller must re-synchronize on any relevant signal edge of the current transmission. The synchronization jump width defines the maximum number of clock cycles a bit period may be shortened or lengthened by one re-synchronization: tSJW = tscl * (sync_jump_width + 1)

Definition at line 23570 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::tseg1 |

[5..0] Time Segment 1 (TSEG1) TSEG1 determine the number of clock cycles per bit period and the location of the sample point, where: tSYNCSEG = 1 * tscl tTSEG1 = tscl * (tseg1

Definition at line 23586 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::tseg2 |

[12..8] Time Segment 2 (TSEG2) TSEG2 determine the number of clock cycles per bit period and the location of the sample point, where: tTSEG2 = tscl * (tseg2 + 1)

Definition at line 23596 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::tx_aborted |

[8..8] Transmission aborted 1 Previously requested transmission is aborted

Definition at line 23470 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::tx_buf_status |

[2..2] Transmit Buffer Status 1 released; the CPU may write a message into the transmit buffer 0 locked; the CPU cannot access the transmit buffer ; a message is either waiting for transmission or is in the process of being transmitted

Definition at line 23452 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::tx_complete |

[3..3] Transmission Complete 1 complete; last requested transmission has been successfully completed 0 incomplete; previously requested transmission is not yet completed

Definition at line 23456 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::tx_err |

[7..0] tx error counter

Definition at line 23699 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::tx_irq |

[1..1] Transmit Interrupt 1 set; this bit is set whenever the transmit buffer status changes from `0-to-1' (released) and the tx_irq_en bit is set within the interrupt enable register 0 reset

Definition at line 23485 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::tx_irq_en |

[1..1] Transmit Interrupt Enable 1 enabled; when a message has been successfully transmitted or the transmit buffer is accessible again (e.g. after an abort transmission command), the CAN controller requests the respective interrupt 0 disabled

Definition at line 23526 of file netx90_app.h.

| __OM uint32_t can_ctrl0_app_Type::tx_request |

[0..0] Transmission Request, self-clearing 1 present; a message shall be transmitted

Definition at line 23420 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::tx_status |

[5..5] Transmit Status 1 transmit; the CAN controller is transmitting a message 0 idle

Definition at line 23461 of file netx90_app.h.

| __IM uint32_t can_ctrl0_app_Type::warning_irq |

[2..2] Error Warning Interrupt 1 set; this bit is set on every change (set and clear) of either the error status or bus status bits and the warning_irq_en bit is set within the interrupt enable register 0 reset

Definition at line 23489 of file netx90_app.h.

| __IOM uint32_t can_ctrl0_app_Type::warning_irq_en |

[2..2] Error Warning Interrupt Enable 1 enabled; if the error or bus status change (see status register), the CAN controller requests the respective interrupt 0 disabled

Definition at line 23531 of file netx90_app.h.