|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

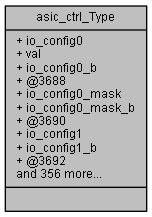

asic_ctrl (asic_ctrl) More...

#include <netx90_app.h>

asic_ctrl (asic_ctrl)

Definition at line 12659 of file netx90_app.h.

| union { ... } |

< (@ 0xFF401200) asic_ctrl Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t asic_ctrl_Type::access_key |

[15..0] Locking access-key for next write access.

Definition at line 13726 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::ahbl_master_ready |

(@ 0x00000090) All AHBL master ready signals. Before stop, reset or clockdisable of any master, check that this bit of the appropriate master is 1. If it is 0, a current access of this master to the system is not finished.

Definition at line 13507 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::ahbl_master_ready_b |

| __IOM uint32_t asic_ctrl_Type::arm_app |

[11..11] enables clock for ARM-APP

Definition at line 13338 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::arm_app_wm |

[27..27] Write mask of arm_app

Definition at line 13353 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_access_key |

(@ 0x000000C0) ASIC Control Locking access-key Register: Writing to any register in the asic_ctrl and other protected address areas (e.g. mmio_ctrl) is only possible after setting the correct key here to avoid unintended changes e.g. by crashed software. -— Changing a control register in the asic_ctrl or in another protected address area is only possible with the following sequence: 1.: Read out the locking access-key from this register. 2.: Write back this locking access-key to this register. 3.: Write

Definition at line 13712 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_access_key_b |

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_clk2rc_length_max |

(@ 0x000000AC) RC-OSC clock period max The maximum RC-OSC clock period in cycles of system clock (10ns).

Definition at line 13616 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_clk2rc_length_max_b |

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_clk2rc_length_min |

(@ 0x000000A8) RC-OSC clock period min The minimum RC-OSC clock period in cycles of system clock (10ns).

Definition at line 13604 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_clk2rc_length_min_b |

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_irq_mask_reset |

(@ 0x000000BC) ASIC_CTRL IRQ mask reset: This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 13691 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_irq_mask_reset_b |

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_irq_mask_set |

(@ 0x000000B8) ASIC_CTRL IRQ mask set: The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ maskq register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating interrupt mask, delete old pending interrupts by writing the same value to bod_irq_raw.

Definition at line 13665 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_irq_mask_set_b |

| __IM uint32_t asic_ctrl_Type::asic_ctrl_irq_masked |

(@ 0x000000B4) ASIC_CTRL masked IRQ: Shows status of masked IRQs.

Definition at line 13648 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_irq_masked_b |

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_irq_raw |

(@ 0x000000B0) ASIC_CTRL raw IRQ: Read access shows status of unmasked IRQs. IRQs are set automatically and reset by writing to this register: Write access with '1' resets the appropriate IRQ. Write access with '0' does not influence this bit.

Definition at line 13628 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_irq_raw_b |

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_netx_unique_id0 |

(@ 0x0000009C) netX unique ID register 0 This register is lockable by asic_ctrl_com.netx_lock-lock_id_regs.

Definition at line 13576 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_netx_unique_id0_b |

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_netx_unique_id1 |

(@ 0x000000A0) netX unique ID register 1 This register is lockable by asic_ctrl_com.netx_lock-lock_id_regs.

Definition at line 13585 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_netx_unique_id1_b |

| __IOM uint32_t asic_ctrl_Type::asic_ctrl_netx_unique_id2 |

(@ 0x000000A4) netX unique ID register 2 This register is lockable by asic_ctrl_com.netx_lock-lock_id_regs.

Definition at line 13594 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::asic_ctrl_netx_unique_id2_b |

| __IOM uint32_t asic_ctrl_Type::bf_align0 |

[31..16] bitField alignment value for aeabi compatibility

[15..12] bitField alignment value for aeabi compatibility

[31..12] bitField alignment value for aeabi compatibility

[7..7] bitField alignment value for aeabi compatibility

[15..13] bitField alignment value for aeabi compatibility

[31..13] bitField alignment value for aeabi compatibility

[15..4] bitField alignment value for aeabi compatibility

[31..4] bitField alignment value for aeabi compatibility

[12..12] bitField alignment value for aeabi compatibility

[31..2] bitField alignment value for aeabi compatibility

[31..1] bitField alignment value for aeabi compatibility

[31..10] bitField alignment value for aeabi compatibility

Definition at line 12772 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::bf_align0 |

[31..20] bitField alignment value for aeabi compatibility

[0..0] bitField alignment value for aeabi compatibility

[31..4] bitField alignment value for aeabi compatibility

Definition at line 13520 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::bf_align1 |

[31..28] bitField alignment value for aeabi compatibility

[23..23] bitField alignment value for aeabi compatibility

[31..16] bitField alignment value for aeabi compatibility

[31..29] bitField alignment value for aeabi compatibility

[31..20] bitField alignment value for aeabi compatibility

[15..14] bitField alignment value for aeabi compatibility

[31..14] bitField alignment value for aeabi compatibility

Definition at line 12928 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::bf_align1 |

[7..2] bitField alignment value for aeabi compatibility

Definition at line 13537 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::bf_align2 |

[28..28] bitField alignment value for aeabi compatibility

Definition at line 13354 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::bf_align2 |

[31..13] bitField alignment value for aeabi compatibility

Definition at line 13552 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::bf_align3 |

[31..30] bitField alignment value for aeabi compatibility

Definition at line 13356 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::bod_fail |

[0..0] raw interrupt state of voltage at BOD pad dropped below threshold

[0..0] set interrupt mask of voltage at BOD pad dropped below threshold

[0..0] reset interrupt mask of voltage at BOD pad dropped below threshold

Definition at line 13636 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::bod_fail |

[0..0] masked interrupt state of voltage at BOD pad dropped below threshold

Definition at line 13652 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::clk25out_oe |

[14..14] Output enable of CLK25OUT pad. When unset (i.e. '0'), pin will be high-z.

Definition at line 12721 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::clk25out_oe_wm |

[30..30] Write mask of clk25out_oe

Definition at line 12740 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::clock_enable0 |

(@ 0x00000068) Global Clock Enable Register: Use this registers to disable modules completely for power saving purposes. Changes will only have an effect if the corresponding bits in the clock_enable_mask-register are set. Note: For low power consumption at power on, all switchable clocks are disabled after reset and must be enabled before module usage. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX

Definition at line 13309 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::clock_enable0_b |

| __IOM uint32_t asic_ctrl_Type::clock_enable0_mask |

(@ 0x0000006C) Global Clock Enable Mask Register: This register can be used to lock the clock_enable0 register. Bits of the clock_enable0 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_lock-lock_register.

Definition at line 13361 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::clock_enable0_mask_b |

| __IOM uint32_t asic_ctrl_Type::clock_enable1 |

(@ 0x00000070) Global Clock Enable Register: Use this registers to disable modules completely for power saving purposes. Changes will only have an effect if the corresponding bits in the clock_enable_mask-register are set. Note: For low power consumption at power on, all switchable clocks are disabled after reset and must be enabled before module usage. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX

Definition at line 13388 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::clock_enable1_b |

| __IOM uint32_t asic_ctrl_Type::clock_enable1_mask |

(@ 0x00000074) Global Clock Enable Mask Register: This register can be used to lock the clock_enable1 register. Bits of the clock_enable1 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_lock-lock_register.

Definition at line 13417 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::clock_enable1_mask_b |

| __IOM uint32_t asic_ctrl_Type::crypt |

[2..2] enables clock for CRYPT units AES and MTGY Note: The HASH and RANDOM units are always on and accessible.

[2..2] enables clock for CRYPT Unit

Definition at line 13404 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::crypt_wm |

[18..18] Write mask of crypt

Definition at line 13410 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::dcdc_enable_n |

[15..15] DCDC converter disable 0: enable DCDC converter 1: disable DCDC converter (should be done, if external core supply is attached)

[15..15] DCDC converter disable

Definition at line 12723 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::dcdc_enable_n_wm |

[31..31] Write mask of dcdc_enable_n

Definition at line 12741 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::dma_app |

[1..1] enables clock for APP DMA-Ctrl

Definition at line 13403 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::dma_app_wm |

[17..17] Write mask of dma_app

Definition at line 13409 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::dma_com |

[10..10] enables clock for COM DMA-Ctrl

Definition at line 13337 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::dma_com_wm |

[26..26] Write mask of dma_com

Definition at line 13352 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::dpm |

[13..13] enables clock for DPM

Definition at line 13340 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::dpm_wm |

[29..29] Write mask of dpm

Definition at line 13355 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::eth_system |

[1..0] Systime for the ethernet system 00: systime_com 01: systime_com_uc 10: systime_app

[1..0] Systime for the ethernet system

Definition at line 13440 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::extbus_to_irq_status |

[1..1] Current status of HIF-Extension Bus Ready Timeout IRQ. Note: This IRQ is controlled/cleared by ext_rdy_cfg register (area hif_asyncmem_ctrl).

Definition at line 13534 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::fb0 |

[6..6] enables clock for fieldbus0 1: use internally generated fb0clk to resample xMAC0 outputs 0: use external xm0_eclk to resample xMAC outputs

[6..6] enables clock for fieldbus0

Definition at line 13329 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::fb0_wm |

[22..22] Write mask of fb0

Definition at line 13348 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::fb1 |

[7..7] enables clock for fieldbus1 1: use internally generated fb1clk to resample xMAC1 outputs 0: use external xm1_eclk to resample xMAC outputs

[7..7] enables clock for fieldbus1

Definition at line 13332 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::fb1_wm |

[23..23] Write mask of fb1

Definition at line 13349 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::gpio_app |

[1..0] Systime for GPIO_APP 00: systime_com 01: systime_com_uc 10: systime_app

[1..0] Systime for GPIO_APP

Definition at line 13485 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::gpio_com |

[1..0] Systime for GPIO_COM

Definition at line 13473 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::id |

[31..0] netX unique ID part 0

[31..0] netX unique ID part 1

[0..0] netX unique ID part 2

Definition at line 13580 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::io_config0 |

(@ 0x00000000) IO Config0 Register: reserved for COM side

Definition at line 12662 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config0_b |

| __IM uint32_t asic_ctrl_Type::io_config0_mask |

(@ 0x00000004) IO Config0 Mask Register: reserved for COM side

Definition at line 12670 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config0_mask_b |

| __IM uint32_t asic_ctrl_Type::io_config1 |

(@ 0x00000008) IO Config1 Register: reserved for COM side

Definition at line 12678 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::io_config10 |

(@ 0x00000050) IO Config10 Register: reserved for COM side

Definition at line 13276 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config10_b |

| __IM uint32_t asic_ctrl_Type::io_config10_mask |

(@ 0x00000054) IO Config10 Mask Register: reserved for COM side

Definition at line 13284 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config10_mask_b |

| __IM uint32_t asic_ctrl_Type::io_config11 |

(@ 0x00000058) IO Config11 Register: reserved for COM side

Definition at line 13292 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config11_b |

| __IM uint32_t asic_ctrl_Type::io_config11_mask |

(@ 0x0000005C) IO Config11 Mask Register: reserved for COM side

Definition at line 13300 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config11_mask_b |

| struct { ... } asic_ctrl_Type::io_config1_b |

| __IM uint32_t asic_ctrl_Type::io_config1_mask |

(@ 0x0000000C) IO Config1 Mask Register: reserved for COM side

Definition at line 12686 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config1_mask_b |

| __IOM uint32_t asic_ctrl_Type::io_config2 |

(@ 0x00000010) IO Config2 Register: Selects of output pin multiplexing. See Excel pinning sheet for details. Changes will only have an effect if the corresponding bits in the io_config2_mask-register are set. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX access-key mechanism; changing this register is only possible by the following sequence: 1.: read out access-key from asic_ctrl_access_key registe

Definition at line 12694 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config2_b |

| __IOM uint32_t asic_ctrl_Type::io_config2_mask |

(@ 0x00000014) IO Config2 Mask Register: This register can be used to lock the special IO configurations for restricted netX devices. Bits of the io_config2 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_l ck-lock_register.

Definition at line 12746 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config2_mask_b |

| __IOM uint32_t asic_ctrl_Type::io_config3 |

(@ 0x00000018) IO Config3 Register: Selects of output pin multiplexing. See Excel pinning sheet for details. Changes will only have an effect if the corresponding bits in the io_config3_mask-register are set. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX access-key mechanism; changing this register is only possible by the following sequence: 1.: read out access-key from asic_ctrl_access_key registe

Definition at line 12777 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config3_b |

| __IOM uint32_t asic_ctrl_Type::io_config3_mask |

(@ 0x0000001C) IO Config3 Mask Register: This register can be used to lock the special IO configurations for restricted netX devices. Bits of the io_config3 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_l ck-lock_register.

Definition at line 12838 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config3_mask_b |

| __IOM uint32_t asic_ctrl_Type::io_config4 |

(@ 0x00000020) IO Config4 Register: Selects of output pin multiplexing. See Excel pinning sheet for details. Changes will only have an effect if the corresponding bits in the io_config4_mask-register are set. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX access-key mechanism; changing this register is only possible by the following sequence: 1.: read out access-key from asic_ctrl_access_key registe

Definition at line 12878 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config4_b |

| __IOM uint32_t asic_ctrl_Type::io_config4_mask |

(@ 0x00000024) IO Config4 Mask Register: This register can be used to lock the special IO configurations for restricted netX devices. Bits of the io_config4 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_l ck-lock_register.

Definition at line 12933 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config4_mask_b |

| __IOM uint32_t asic_ctrl_Type::io_config5 |

(@ 0x00000028) IO Config5 Register: Selects of output pin multiplexing. See Excel pinning sheet for details. Changes will only have an effect if the corresponding bits in the io_config5_mask-register are set. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX access-key mechanism; changing this register is only possible by the following sequence: 1.: read out access-key from asic_ctrl_access_key registe

Definition at line 12971 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config5_b |

| __IOM uint32_t asic_ctrl_Type::io_config5_mask |

(@ 0x0000002C) IO Config5 Mask Register: This register can be used to lock the special IO configurations for restricted netX devices. Bits of the io_config5 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_l ck-lock_register.

Definition at line 13010 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config5_mask_b |

| __IOM uint32_t asic_ctrl_Type::io_config6 |

(@ 0x00000030) IO Config6 Register: Selects of output pin multiplexing. See Excel pinning sheet for details. Changes will only have an effect if the corresponding bits in the io_config6_mask-register are set. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX access-key mechanism; changing this register is only possible by the following sequence: 1.: read out access-key from asic_ctrl_access_key registe

Definition at line 13035 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config6_b |

| __IOM uint32_t asic_ctrl_Type::io_config6_mask |

(@ 0x00000034) IO Config6 Mask Register: This register can be used to lock the special IO configurations for restricted netX devices. Bits of the io_config6 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_l ck-lock_register.

Definition at line 13084 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config6_mask_b |

| __IOM uint32_t asic_ctrl_Type::io_config7 |

(@ 0x00000038) IO Config7 Register: Selects of output pin multiplexing. See Excel pinning sheet for details. Changes will only have an effect if the corresponding bits in the io_config7_mask-register are set. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX access-key mechanism; changing this register is only possible by the following sequence: 1.: read out access-key from asic_ctrl_access_key registe

Definition at line 13114 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config7_b |

| __IOM uint32_t asic_ctrl_Type::io_config7_mask |

(@ 0x0000003C) IO Config7 Mask Register: This register can be used to lock the special IO configurations for restricted netX devices. Bits of the io_config7 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_l ck-lock_register.

Definition at line 13165 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config7_mask_b |

| __IOM uint32_t asic_ctrl_Type::io_config8 |

(@ 0x00000040) IO Config8 Register: Selects of output pin multiplexing. See Excel pinning sheet for details. Changes will only have an effect if the corresponding bits in the io_config8_mask-register are set. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX access-key mechanism; changing this register is only possible by the following sequence: 1.: read out access-key from asic_ctrl_access_key registe

Definition at line 13190 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config8_b |

| __IOM uint32_t asic_ctrl_Type::io_config8_mask |

(@ 0x00000044) IO Config8 Mask Register: This register can be used to lock the special IO configurations for restricted netX devices. Bits of the io_config8 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_l ck-lock_register.

Definition at line 13224 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config8_mask_b |

| __IOM uint32_t asic_ctrl_Type::io_config9 |

(@ 0x00000048) IO Config9 Register: Selects of output pin multiplexing. See Excel pinning sheet for details. Changes will only have an effect if the corresponding bits in the io_config9_mask-register are set. This register is a write mask register, i.e. lower 16 bits are only writeable, if corresponding upper bits are set. This register is protected by the netX access-key mechanism; changing this register is only possible by the following sequence: 1.: read out access-key from asic_ctrl_access_key registe

Definition at line 13242 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config9_b |

| __IOM uint32_t asic_ctrl_Type::io_config9_mask |

(@ 0x0000004C) IO Config9 Mask Register: This register can be used to lock the special IO configurations for restricted netX devices. Bits of the io_config9 register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_l ck-lock_register.

Definition at line 13261 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::io_config9_mask_b |

| __IOM uint32_t asic_ctrl_Type::ipc |

[3..3] enables clock for IPC Units (OSAC/NFIFO)

Definition at line 13406 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::ipc_wm |

[19..19] Write mask of ipc

Definition at line 13411 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::len |

[9..0] Minimum length of RC-clock period: This register writable, but it can also be changed by hardware. Set to 0x3ff to find a new minimum value.

[9..0] max length of RC-clock period This register writable, but it can also be changed by hardware. Set to 0 to find a new maximum value.

Definition at line 13608 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::netx_version |

(@ 0x00000098) netX Revision Register: This register contains information about netX hardware and bootloader revision. This register is lockable by asic_ctrl_com.netx_ ock-lock_id_regs.

[31..0] netX revision number: Hardware reset values of netX version register is: 0x01: netx100, netx500 0x01: netx50 0x02: netx5_mpw 0x41: netx5 0x50: netx10 0x05: netx51/52 0x06: reserved 0x07: netx6 0x08: netx4000_relaxed 0x09: reserved 0x0a: netx4000 0x0b: reserved 0x0c: netx90_mpw 0x0d: netx90 Further netX revisions should increment (next: 0x0e). This register is changed to Hilscher netX bootloader revision by ROM-code: Hardware reset values should differ from Hilscher values! netX50 revision number starts wit

Definition at line 13557 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::netx_version_b |

| __IM uint32_t asic_ctrl_Type::pll_bypass |

[10..10] Testmode 'pll_bypass' is activated by TESTDECODER JTAG TAP controller (clk_test is selected in this case) or by the bit pll_bypass of the system_ctrl register in ASIC_CTRL_COM ist set -> 400MHz-PLL is bypassed, PLL output is unused, 400MHz-Clocks (clk400, clk400_2sdram) are directly connected to the RC-OSC clock.

Definition at line 13540 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::pll_fast |

[3..3] raw interrupt state of CLKSUP detected PLL too fast or RC-OSC too slow

[3..3] set interrupt mask of CLKSUP detected PLL too fast or RC-OSC too slow

[3..3] reset interrupt mask of CLKSUP detected PLL too fast or RC-OSC too slow

Definition at line 13641 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::pll_fast |

[3..3] masked interrupt state of CLKSUP detected PLL too fast or RC-OSC too slow

Definition at line 13658 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::pll_noclk |

[1..1] raw interrupt state of CLKSUP detected no clock at PLL

[1..1] set interrupt mask of CLKSUP detected no clock at PLL

[1..1] reset interrupt mask of CLKSUP detected no clock at PLL

Definition at line 13638 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::pll_noclk |

[1..1] masked interrupt state of CLKSUP detected no clock at PLL

Definition at line 13654 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::pll_slow |

[2..2] raw interrupt state of CLKSUP detected PLL too slow or RC-OSC too fast

[2..2] set interrupt mask of CLKSUP detected PLL too slow or RC-OSC too fast

[2..2] reset interrupt mask of CLKSUP detected PLL too slow or RC-OSC too fast

Definition at line 13639 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::pll_slow |

[2..2] masked interrupt state of CLKSUP detected PLL too slow or RC-OSC too fast

Definition at line 13656 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::pw_bod_ok |

[9..9] Power watch brown-out detection status

Definition at line 13539 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::quick_count |

[11..11] Testmode 'quick_count' is activated by BSCAN JTAG TAP controller -> diverse internal counters count faster (RTC-clock-divider, PLL-stby-controller,...)

Definition at line 13546 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::RESERVED[2] |

Definition at line 13306 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::RESERVED1 |

Definition at line 13461 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::rpec0 |

[0..0] enables clock for rPEC0

Definition at line 13323 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::rpec0_wm |

[16..16] Write mask of rpec0

Definition at line 13342 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::rpec1 |

[1..1] enables clock for rPEC1

Definition at line 13324 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::rpec1_wm |

[17..17] Write mask of rpec1

Definition at line 13343 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_arm_trace_cfg |

[1..0] select pins for CoreSight Tracing 00: Disable Trace: sel_trace = 0, sel_trace_d[3:0] = 0000 01: Trace with 1 data line: sel_trace = 1, sel_trace_d[3:0] = 0001 10: Trace with 2 data lines: sel_trace = 1, sel_trace_d[3:0] = 0011 11: Trace with 4 data lines: sel_trace = 1, sel_trace_d[3:0] = 1111

[1..0] select pins for CoreSight Tracing

Definition at line 13203 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_arm_trace_cfg_wm |

[17..16] Write mask of sel_arm_trace_cfg

Definition at line 13216 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_bga2 |

[3..3] select *_bga2 pins in pinning table: This is intended for a second bondout version using external Ethernet PHY. If sel_bga2 is active, output enable of pin MII0_TXEN will be inactive, all other *_bga2 pins are inputs.

[3..3] select *_bga2 pins of 2nd BGA package

Definition at line 13211 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_bga2_wm |

[19..19] Write mask of sel_bga2

Definition at line 13218 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_biss0 |

[12..12] select pads BISS ch 0 (s. pinning table)

Definition at line 12814 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_biss0_mo |

[13..13] select pad BISS ch 0 MO (s. pinning table)

Definition at line 12815 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_biss0_mo_wm |

[29..29] Write mask of sel_biss0_mo

Definition at line 12831 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_biss0_wm |

[28..28] Write mask of sel_biss0

Definition at line 12830 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_biss1 |

[14..14] select pads BISS ch 1 (s. pinning table)

Definition at line 12816 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_biss1_mo |

[15..15] select pad BISS ch 1 MO (s. pinning table)

Definition at line 12817 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_biss1_mo_wm |

[31..31] Write mask of sel_biss1_mo

Definition at line 12833 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_biss1_wm |

[30..30] Write mask of sel_biss1

Definition at line 12832 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_can0_app |

[10..10] select pad for can0_app (s. pinning table) and deactivate this function via MMIOs

Definition at line 12911 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_can0_app_wm |

[26..26] Write mask of sel_can0_app

Definition at line 12926 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_can1_app |

[11..11] select pad for can1_app (s. pinning table) and deactivate this function via MMIOs

Definition at line 12913 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_can1_app_wm |

[27..27] Write mask of sel_can1_app

Definition at line 12927 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_endat0 |

[8..8] select pads EnDAT ch 0 (s. pinning table)

Definition at line 12806 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_endat0_devel |

[9..9] select pads EnDAT ch 0 development function (s. pinning table) Note: EnDAT development function outputs are delayed by one sys-clk.

[9..9] select pads EnDAT ch 0 development function (s. pinning table)

Definition at line 12807 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_endat0_devel_wm |

[25..25] Write mask of sel_endat0_devel

Definition at line 12827 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_endat0_wm |

[24..24] Write mask of sel_endat0

Definition at line 12826 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_endat1 |

[10..10] select pads EnDAT ch 1 (s. pinning table)

Definition at line 12810 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_endat1_devel |

[11..11] select pads EnDAT ch 1 development function (s. pinning table) Note: EnDAT development function outputs are delayed by one sys-clk.

[11..11] select pads EnDAT ch 1 development function (s. pinning table)

Definition at line 12811 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_endat1_devel_wm |

[27..27] Write mask of sel_endat1_devel

Definition at line 12829 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_endat1_wm |

[26..26] Write mask of sel_endat1

Definition at line 12828 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_ephy0 |

[6..6] connect PHY0 MII to external MAC (s. pinning table)

Definition at line 12713 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_ephy0_wm |

[22..22] Write mask of sel_ephy0

Definition at line 12732 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_ephy1 |

[7..7] connect PHY1 MII to external MAC (s. pinning table)

Definition at line 12714 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_ephy1_wm |

[23..23] Write mask of sel_ephy1

Definition at line 12733 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_ephy_mdio |

[8..8] connect PHY MDIO to external pads (s. pinning table)

Definition at line 12715 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_ephy_mdio_wm |

[24..24] Write mask of sel_ephy_mdio

Definition at line 12734 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_eth_cfg |

[4..0] select connection of ETH MII pins: 0: no select 1: select pads for ETH RMII (rxd[1:0],rxdv,rxer,txclk,txd[1:0],txen) (s. pinning table: sel_eth_5,2,1 will be active) 2: select pads for ETH RX only mode (rxclk, rxd[3:0],rxdv,rxer) (s. pinning table: sel_eth_5,3,2,0 will be active) 3: select pads for ETH minimum data transfer in phy mode (rxd,rxdv,txclk,txd,txen) (s. pinning table: sel_eth_4:1 will be active) 4: select also pads for ETH rxclk pin for mac mode (rxclk) (s. pinning table: sel_eth_4:0 will be ac

[4..0] select connection of ETH MII pins:

Definition at line 13127 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_eth_cfg_wm |

[20..16] Write mask of sel_eth_cfg

Definition at line 13152 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_eth_mdio |

[6..5] select connection for MIIMU MDIO interface used by ETH 00: ETH MIIMU not connected to IOs but the multiplexmatrix can be used for it. 01: connect to external eth_mdio default position (s. pinning table sel_eth_mdio) 10: connect to external eth_mdio position B (s pinning table sel_eth_b_mdio) pins (s pinning table) 11: connect to internal PHY

[6..5] select connection for MIIMU MDIO interface used by ETH

Definition at line 13136 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_eth_mdio_wm |

[22..21] Write mask of sel_eth_mdio

Definition at line 13153 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_extphy |

[2..2] select *_extphy pins in pinning table: This is intended to combine external PHYs with SDRAM.

[2..2] select different positions in case of external PHY should be connected in parallel with SDRAM.

Definition at line 13209 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_extphy_wm |

[18..18] Write mask of sel_extphy

Definition at line 13217 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_fo0 |

[9..9] select Fiber Optics of PHY0 (s. pinning table)

Definition at line 12716 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_fo0_wm |

[25..25] Write mask of sel_fo0

Definition at line 12735 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_fo1 |

[10..10] select Fiber Optics of PHY1 (s. pinning table)

Definition at line 12717 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_fo1_wm |

[26..26] Write mask of sel_fo1

Definition at line 12736 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio0 |

[0..0] select pad for gpio0 (s. pinning table) and deactivate this function via MMIOs

Definition at line 12790 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio0_wm |

[16..16] Write mask of sel_gpio0

Definition at line 12818 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio1 |

[1..1] select pad for gpio1 (s. pinning table) and deactivate this function via MMIOs

Definition at line 12792 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio10 |

[2..2] select pad for gpio10 (s. pinning table)

Definition at line 12709 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio10_wm |

[18..18] Write mask of sel_gpio10

Definition at line 12728 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio11 |

[3..3] select pad for gpio11 (s. pinning table)

Definition at line 12710 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio11_wm |

[19..19] Write mask of sel_gpio11

Definition at line 12729 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio1_wm |

[17..17] Write mask of sel_gpio1

Definition at line 12819 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio2 |

[2..2] select pad for gpio2 (s. pinning table) and deactivate this function via MMIOs

Definition at line 12794 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio2_wm |

[18..18] Write mask of sel_gpio2

Definition at line 12820 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio3 |

[3..3] select pad for gpio3 (s. pinning table) and deactivate this function via MMIOs

Definition at line 12796 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio3_wm |

[19..19] Write mask of sel_gpio3

Definition at line 12821 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio4 |

[4..4] select pad for gpio4 (s. pinning table) and deactivate this function via MMIOs

Definition at line 12798 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio4_wm |

[20..20] Write mask of sel_gpio4

Definition at line 12822 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio5 |

[5..5] select pad for gpio5 (s. pinning table) and deactivate this function via MMIOs

Definition at line 12800 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio5_wm |

[21..21] Write mask of sel_gpio5

Definition at line 12823 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio6 |

[6..6] select pad for gpio6 (s. pinning table) and deactivate this function via MMIOs

Definition at line 12802 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio6_wm |

[22..22] Write mask of sel_gpio6

Definition at line 12824 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio7 |

[7..7] select pad for gpio7 (s. pinning table) and deactivate this function via MMIOs

Definition at line 12804 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio7_wm |

[23..23] Write mask of sel_gpio7

Definition at line 12825 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio8 |

[0..0] select pad for gpio8 (s. pinning table)

Definition at line 12707 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio8_wm |

[16..16] Write mask of sel_gpio8

Definition at line 12726 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio9 |

[1..1] select pad for gpio9 (s. pinning table)

Definition at line 12708 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_gpio9_wm |

[17..17] Write mask of sel_gpio9

Definition at line 12727 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_i2c0_com |

[11..11] select pads for i2c0_com (s. pinning table)

Definition at line 12718 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_i2c0_com_wm |

[27..27] Write mask of sel_i2c0_com

Definition at line 12737 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_i2c1_com |

[12..12] select pads for i2c1_com (s. pinning table)

Definition at line 12719 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_i2c1_com_wm |

[28..28] Write mask of sel_i2c1_com

Definition at line 12738 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_i2c_app |

[0..0] select pads for i2c_app (s. pinning table) and deactivate this function via MMIOs

Definition at line 12891 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_i2c_app_wm |

[16..16] Write mask of sel_i2c_app

Definition at line 12916 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link0 |

[0..0] select pads for IO-Link0 (s. pinning table)

Definition at line 13048 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link0_wm |

[16..16] Write mask of sel_io_link0

Definition at line 13064 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link0b |

[9..9] select pads for IO-Link0 at position B (s. pinning table)

Definition at line 13144 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link0b_wm |

[25..25] Write mask of sel_io_link0b

Definition at line 13156 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link1 |

[1..1] select pads for IO-Link1 (s. pinning table)

Definition at line 13049 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link1_wm |

[17..17] Write mask of sel_io_link1

Definition at line 13065 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link1b |

[10..10] select pads for IO-Link1 at position B (s. pinning table)

Definition at line 13145 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link1b_wm |

[26..26] Write mask of sel_io_link1b

Definition at line 13157 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link2 |

[2..2] select pads for IO-Link2 (s. pinning table)

Definition at line 13050 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link2_wm |

[18..18] Write mask of sel_io_link2

Definition at line 13066 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link3 |

[3..3] select pads for IO-Link3 (s. pinning table)

Definition at line 13051 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link3_wm |

[19..19] Write mask of sel_io_link3

Definition at line 13067 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link4 |

[4..4] select pads for IO-Link4 (s. pinning table)

Definition at line 13052 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link4_wm |

[20..20] Write mask of sel_io_link4

Definition at line 13068 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link5 |

[5..5] select pads for IO-Link5 (s. pinning table)

Definition at line 13053 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link5_wm |

[21..21] Write mask of sel_io_link5

Definition at line 13069 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link6 |

[6..6] select pads for IO-Link6 (s. pinning table)

Definition at line 13054 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link6_wm |

[22..22] Write mask of sel_io_link6

Definition at line 13070 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link7 |

[7..7] select pads for IO-Link7 (s. pinning table)

Definition at line 13055 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link7_wm |

[23..23] Write mask of sel_io_link7

Definition at line 13071 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup0 |

[8..8] select pads for IO-Link0 Wakeup (s. pinning table)

Definition at line 13056 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup0_wm |

[24..24] Write mask of sel_io_link_wakeup0

Definition at line 13072 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup0b |

[11..11] select pads for IO-Link0 Wakeup at position B (s. pinning table)

Definition at line 13147 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup0b_wm |

[27..27] Write mask of sel_io_link_wakeup0b

Definition at line 13158 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup1 |

[9..9] select pads for IO-Link1 Wakeup (s. pinning table)

Definition at line 13057 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup1_wm |

[25..25] Write mask of sel_io_link_wakeup1

Definition at line 13073 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup1b |

[12..12] select pads for IO-Link1 Wakeup at position B (s. pinning table)

Definition at line 13149 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup1b_wm |

[28..28] Write mask of sel_io_link_wakeup1b

Definition at line 13159 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup2 |

[10..10] select pads for IO-Link2 Wakeup (s. pinning table)

Definition at line 13058 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup2_wm |

[26..26] Write mask of sel_io_link_wakeup2

Definition at line 13074 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup3 |

[11..11] select pads for IO-Link3 Wakeup (s. pinning table)

Definition at line 13059 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup3_wm |

[27..27] Write mask of sel_io_link_wakeup3

Definition at line 13075 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup4 |

[12..12] select pads for IO-Link4 Wakeup (s. pinning table)

Definition at line 13060 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup4_wm |

[28..28] Write mask of sel_io_link_wakeup4

Definition at line 13076 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup5 |

[13..13] select pads for IO-Link5 Wakeup (s. pinning table)

Definition at line 13061 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup5_wm |

[29..29] Write mask of sel_io_link_wakeup5

Definition at line 13077 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup6 |

[14..14] select pads for IO-Link6 Wakeup (s. pinning table)

Definition at line 13062 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup6_wm |

[30..30] Write mask of sel_io_link_wakeup6

Definition at line 13078 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup7 |

[15..15] select pads for IO-Link7 Wakeup (s. pinning table)

Definition at line 13063 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_io_link_wakeup7_wm |

[31..31] Write mask of sel_io_link_wakeup7

Definition at line 13079 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled10 |

[14..14] select pad for mled10 (s. pinning table)

Definition at line 12993 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled10_wm |

[30..30] Write mask of sel_mled10

Definition at line 13004 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled11 |

[15..15] select pad for mled11 (s. pinning table)

Definition at line 12994 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled11_wm |

[31..31] Write mask of sel_mled11

Definition at line 13005 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled4 |

[8..8] select pad for mled4 (s. pinning table)

Definition at line 12987 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled4_wm |

[24..24] Write mask of sel_mled4

Definition at line 12998 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled5 |

[9..9] select pad for mled5 (s. pinning table)

Definition at line 12988 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled5_wm |

[25..25] Write mask of sel_mled5

Definition at line 12999 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled6 |

[10..10] select pad for mled6 (s. pinning table)

Definition at line 12989 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled6_wm |

[26..26] Write mask of sel_mled6

Definition at line 13000 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled7 |

[11..11] select pad for mled7 (s. pinning table)

Definition at line 12990 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled7_wm |

[27..27] Write mask of sel_mled7

Definition at line 13001 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled8 |

[12..12] select pad for mled8 (s. pinning table)

Definition at line 12991 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled8_wm |

[28..28] Write mask of sel_mled8

Definition at line 13002 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled9 |

[13..13] select pad for mled9 (s. pinning table)

Definition at line 12992 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mled9_wm |

[29..29] Write mask of sel_mled9

Definition at line 13003 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mpwm |

[5..0] select pad for mpwm (s. pinning table)

Definition at line 12984 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mpwm_brake |

[6..6] select pad for mpwm_brake (s. pinning table)

Definition at line 12985 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mpwm_brake_wm |

[22..22] Write mask of sel_mpwm_brake

Definition at line 12996 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_mpwm_wm |

[21..16] Write mask of sel_mpwm

Definition at line 12995 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_phy_devel |

[5..5] select PHY development outputs (s. pinning table)

Definition at line 12712 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_phy_devel_wm |

[21..21] Write mask of sel_phy_devel

Definition at line 12731 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_pio_app |

[15..0] select pads for pio_app15:0

Definition at line 13255 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_pio_app_wm |

[31..16] Write mask of sel_pio_app

Definition at line 13256 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi0_app |

[5..5] select pads for spi0_app (s. pinning table) and deactivate this function via MMIOs

Definition at line 12901 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi0_app_cs1 |

[6..6] select pad for 2nd chip select of spi0_app (s. pinning table)

Definition at line 12903 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi0_app_cs1_wm |

[22..22] Write mask of sel_spi0_app_cs1

Definition at line 12922 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi0_app_wm |

[21..21] Write mask of sel_spi0_app

Definition at line 12921 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi2_app |

[7..7] select pads for spi2_app (s. pinning table) and deactivate this function via MMIOs

Definition at line 12905 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi2_app_cs1 |

[8..8] select pad for 2nd chip select of spi2_app (s. pinning table)

Definition at line 12907 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi2_app_cs1_wm |

[24..24] Write mask of sel_spi2_app_cs1

Definition at line 12924 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi2_app_cs2 |

[9..9] select pad for 3rd chip select of spi2_app (s. pinning table)

Definition at line 12909 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi2_app_cs2_wm |

[25..25] Write mask of sel_spi2_app_cs2

Definition at line 12925 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_spi2_app_wm |

[23..23] Write mask of sel_spi2_app

Definition at line 12923 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_sqi_cs1 |

[7..7] select pad for 2nd chip select of sqi (s. pinning table)

Definition at line 13142 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_sqi_cs1_wm |

[23..23] Write mask of sel_sqi_cs1

Definition at line 13154 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_sqi_cs2 |

[8..8] select pad for 3rd chip select of sqi (s. pinning table)

Definition at line 13143 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_sqi_cs2_wm |

[24..24] Write mask of sel_sqi_cs2

Definition at line 13155 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_app |

[1..1] select pads for uart_app (s. pinning table) and deactivate this function via MMIOs

Definition at line 12893 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_app_rctsn |

[2..2] select pads for uart_app RTS/CTS signals (s. pinning table) and deactivate this function via MMIOs

Definition at line 12895 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_app_rctsn_wm |

[18..18] Write mask of sel_uart_app_rctsn

Definition at line 12918 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_app_wm |

[17..17] Write mask of sel_uart_app

Definition at line 12917 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_rctsn |

[13..13] select pads for uart RTS/CTS signals (s. pinning table)

Definition at line 12720 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_rctsn_wm |

[29..29] Write mask of sel_uart_rctsn

Definition at line 12739 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_xpic_app |

[3..3] select pads for uart_xpic_app (s. pinning table) and deactivate this function via MMIOs

Definition at line 12897 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_xpic_app_rctsn |

[4..4] select pads for uart_xpic_app RTS/CTS signals (s. pinning table) and deactivate this function via MMIOs

Definition at line 12899 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_xpic_app_rctsn_wm |

[20..20] Write mask of sel_uart_xpic_app_rctsn

Definition at line 12920 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_uart_xpic_app_wm |

[19..19] Write mask of sel_uart_xpic_app

Definition at line 12919 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_xc_trigger0_hif_sirq |

[4..4] select xc_trigger0 on HIF_SIRQ (s. pinning table)

Definition at line 12711 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::sel_xc_trigger0_hif_sirq_wm |

[20..20] Write mask of sel_xc_trigger0_hif_sirq

Definition at line 12730 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::system_status |

(@ 0x00000094) netX System Status Register. This register provides information of special netX system events, e.g: System related interrupt activity, Abort activity. Abort or IRQ status flag can be cleared by writing a '1' to the appropriate bits.

Definition at line 13525 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::system_status_b |

| __IOM uint32_t asic_ctrl_Type::systime_eth_system_ctrl |

(@ 0x00000078) Select systime for the ethernet system Changes will only have an effect if the corresponding bits in the systime_eth_system_ctrl_mask-register are set.

Definition at line 13434 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::systime_eth_system_ctrl_b |

| __IOM uint32_t asic_ctrl_Type::systime_eth_system_ctrl_mask |

(@ 0x0000007C) Select systime for the ethernet system (mask register) This register can be used to lock the systime_eth_system_ctrl register. Bits of the systime_eth_system_ctrl register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_lock-lock_regis er.

Definition at line 13447 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::systime_eth_system_ctrl_mask_b |

| __IOM uint32_t asic_ctrl_Type::systime_gpio_app_ctrl |

(@ 0x00000088) Select systime for GPIO_APP Changes will only have an effect if the corresponding bits in the systime_gpio_app_ctrl_mask-register are set.

Definition at line 13479 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::systime_gpio_app_ctrl_b |

| __IOM uint32_t asic_ctrl_Type::systime_gpio_app_ctrl_mask |

(@ 0x0000008C) Select systime for GPIO_APP (mask register) This register can be used to lock the systime_gpio_app_ctrl register. Bits of the systime_gpio_app_ctrl register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_lock-lock_regis er.

Definition at line 13492 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::systime_gpio_app_ctrl_mask_b |

| __IOM uint32_t asic_ctrl_Type::systime_gpio_com_ctrl_mask |

(@ 0x00000084) Select systime for GPIO_COM (mask register) This register can be used to lock the systime_gpio_com_ctrl register. Bits of the systime_gpio_com_ctrl register can only be modified if the corresponding mask bits in this register are set. This register is lockable by asic_ctrl_com.netx_lock-lock_regis er.

Definition at line 13464 of file netx90_app.h.

| struct { ... } asic_ctrl_Type::systime_gpio_com_ctrl_mask_b |

| __IM uint32_t asic_ctrl_Type::testmode |

[8..8] sampled netx TESTMODE input for production test purpose

Definition at line 13538 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::tpec0 |

[2..2] enables clock for tPEC0

Definition at line 13325 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::tpec0_wm |

[18..18] Write mask of tpec0

Definition at line 13344 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::tpec1 |

[3..3] enables clock for tPEC1

Definition at line 13326 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::tpec1_wm |

[19..19] Write mask of tpec1

Definition at line 13345 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::val |

[31..0] reserved value

[19..0] netx ahbl_master readys M_DPM0 0 M_DPM1 1 M_XC01_d 2 M_XC01_s 3 M_ADC_MASTER 4 M_IPC_MASTER 5 M_IDPM_MASTER 6 M_DEBUG_MASTER 7 M_XPIC_COM_d 8 M_XPIC_COM_i 9 M_XPIC_APP_d 10 M_XPIC_APP_i 11 M_ARM_COM_d 12 M_ARM_COM_i 13 M_ARM_COM_s 14 M_ARM_APP_d 15 M_ARM_APP_i 16 M_ARM_APP_s 17 M_DMAC_COM 18 M_DMAC_APP 19

Definition at line 12665 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xc_misc |

[8..8] enables clock for misc. XC logic (XC-DMAC, XC-SR, XC-BUFMAN

Definition at line 13335 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xc_misc_wm |

[24..24] Write mask of xc_misc

Definition at line 13350 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xmac0 |

[4..4] enables clock for xMAC0

Definition at line 13327 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xmac0_wm |

[20..20] Write mask of xmac0

Definition at line 13346 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xmac1 |

[5..5] enables clock for xMAC1

Definition at line 13328 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xmac1_wm |

[21..21] Write mask of xmac1

Definition at line 13347 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xpic0 |

[9..9] enables clock for XPIC0

Definition at line 13336 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xpic0_wm |

[25..25] Write mask of xpic0

Definition at line 13351 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xpic1 |

[0..0] enables clock for XPIC1

Definition at line 13402 of file netx90_app.h.

| __IOM uint32_t asic_ctrl_Type::xpic1_wm |

[16..16] Write mask of xpic1

Definition at line 13408 of file netx90_app.h.

| __IM uint32_t asic_ctrl_Type::xtal_ok |

[12..12] XTAL status signal of disclock. If '1', the PLL can be powered up. -> diverse internal counters count faster (RTC-clock-divider, PLL-stby-controller,...)

Definition at line 13549 of file netx90_app.h.