|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

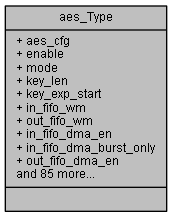

aes (aes) More...

#include <netx90_app.h>

aes (aes)

Definition at line 2781 of file netx90_app.h.

| union { ... } |

< (@ 0xFF080300) aes Structure

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| union { ... } |

| __IOM uint32_t aes_Type::aes_cfg |

(@ 0x00000000) AES config register

Definition at line 2784 of file netx90_app.h.

| struct { ... } aes_Type::aes_cfg_b |

| __OM uint32_t aes_Type::aes_din |

(@ 0x00000038) AES FIFO input Unlike all other registers, this address can be written with DWord(32 Bit), Word(16 Bit) or Byte acccss. The FIFO controller will automatically collect data and start AES-calculation, if enough data (4 DWords) are collected.

Definition at line 3059 of file netx90_app.h.

| struct { ... } aes_Type::aes_din_b |

| __IM uint32_t aes_Type::aes_dout |

(@ 0x0000003C) AES FIFO output

Definition at line 3072 of file netx90_app.h.

| struct { ... } aes_Type::aes_dout_b |

| __IM uint32_t aes_Type::aes_irq_masked |

(@ 0x0000000C) AES masked IRQ: Shows status of masked IRQs.

Definition at line 2886 of file netx90_app.h.

| struct { ... } aes_Type::aes_irq_masked_b |

| __IOM uint32_t aes_Type::aes_irq_msk_reset |

(@ 0x00000014) AES IRQ mask reset: This is the corresponding reset mask to disable interrupt requests for corresponding interrupt sources: Write access with '1' resets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask.

Definition at line 2958 of file netx90_app.h.

| struct { ... } aes_Type::aes_irq_msk_reset_b |

| __IOM uint32_t aes_Type::aes_irq_msk_set |

(@ 0x00000010) AES IRQ mask set: The IRQ mask enables interrupt requests for corresponding interrupt sources. As its bits might be changed by different software tasks, the IRQ mask register is not writable directly, but by set and reset masks: Write access with '1' sets interrupt mask bit. Write access with '0' does not influence this bit. Read access shows actual interrupt mask. Attention: Before activating interrupt mask, delete old pending interrupts by writing the same value to crypt_aes_irq_raw.

Definition at line 2917 of file netx90_app.h.

| struct { ... } aes_Type::aes_irq_msk_set_b |

| __IOM uint32_t aes_Type::aes_irq_raw |

(@ 0x00000008) AES raw IRQ: Read access shows status of unmasked IRQs. IRQs are set automatically and reset by writing to this register: Write access with '1' resets the appropriate IRQ. Write access with '0' does not influence this bit.

Definition at line 2846 of file netx90_app.h.

| struct { ... } aes_Type::aes_irq_raw_b |

| __IOM uint32_t aes_Type::aes_key0 |

(@ 0x00000018) AES key register 0

Definition at line 2995 of file netx90_app.h.

| struct { ... } aes_Type::aes_key0_b |

| __IOM uint32_t aes_Type::aes_key1 |

(@ 0x0000001C) AES key register 1

Definition at line 3003 of file netx90_app.h.

| struct { ... } aes_Type::aes_key1_b |

| __IOM uint32_t aes_Type::aes_key2 |

(@ 0x00000020) AES key register 2

Definition at line 3011 of file netx90_app.h.

| struct { ... } aes_Type::aes_key2_b |

| __IOM uint32_t aes_Type::aes_key3 |

(@ 0x00000024) AES key register 3

Definition at line 3019 of file netx90_app.h.

| struct { ... } aes_Type::aes_key3_b |

| __IOM uint32_t aes_Type::aes_key4 |

(@ 0x00000028) AES key register 4

Definition at line 3027 of file netx90_app.h.

| struct { ... } aes_Type::aes_key4_b |

| __IOM uint32_t aes_Type::aes_key5 |

(@ 0x0000002C) AES key register 5

Definition at line 3035 of file netx90_app.h.

| struct { ... } aes_Type::aes_key5_b |

| __IOM uint32_t aes_Type::aes_key6 |

(@ 0x00000030) AES key register 6

Definition at line 3043 of file netx90_app.h.

| struct { ... } aes_Type::aes_key6_b |

| __IOM uint32_t aes_Type::aes_key7 |

(@ 0x00000034) AES key register 7

Definition at line 3051 of file netx90_app.h.

| struct { ... } aes_Type::aes_key7_b |

| __IM uint32_t aes_Type::aes_stat |

(@ 0x00000004) AES status register

Definition at line 2813 of file netx90_app.h.

| struct { ... } aes_Type::aes_stat_b |

| __IOM uint32_t aes_Type::bf_align0 |

[31..21] bitField alignment value for aeabi compatibility

[31..16] bitField alignment value for aeabi compatibility

Definition at line 2808 of file netx90_app.h.

| __IM uint32_t aes_Type::bf_align0 |

[31..28] bitField alignment value for aeabi compatibility

[31..16] bitField alignment value for aeabi compatibility

Definition at line 2841 of file netx90_app.h.

| __IOM uint32_t aes_Type::enable |

[0..0] Enables the AES core operation.

Definition at line 2787 of file netx90_app.h.

| __IOM uint32_t aes_Type::in_fifo_dma_burst_only |

[18..18] Generate DMAC burst signal only (input FIFO). When set to '1' the DMAC logic will only generate burst requests to the DMAC. This is to overcome limitations of the current DMA controller implementation that only accepts burst requests for DMAC controlled memory to peripheral transfers.

Definition at line 2798 of file netx90_app.h.

| __IOM uint32_t aes_Type::in_fifo_dma_en |

[17..17] Enable DMAC control signals for the input FIFO

Definition at line 2797 of file netx90_app.h.

| __IM uint32_t aes_Type::in_fifo_empty |

| __IOM uint32_t aes_Type::in_fifo_empty |

[3..3] Input FIFO is empty

Definition at line 2859 of file netx90_app.h.

| __IM uint32_t aes_Type::in_fifo_fill |

[8..2] Fill level of input FIFO in bytes (0..64)

Definition at line 2819 of file netx90_app.h.

| __IM uint32_t aes_Type::in_fifo_full |

| __IOM uint32_t aes_Type::in_fifo_full |

[5..5] Input FIFO is full

Definition at line 2861 of file netx90_app.h.

| __IM uint32_t aes_Type::in_fifo_not_empty |

[10..10] Input FIFO is not empty

[4..4] Input FIFO is not empty

Definition at line 2821 of file netx90_app.h.

| __IOM uint32_t aes_Type::in_fifo_not_empty |

[4..4] Input FIFO is not empty

Definition at line 2860 of file netx90_app.h.

| __IM uint32_t aes_Type::in_fifo_not_full |

[12..12] Input FIFO is not full

[6..6] Input FIFO is not full

Definition at line 2823 of file netx90_app.h.

| __IOM uint32_t aes_Type::in_fifo_not_full |

[6..6] Input FIFO is not full

Definition at line 2862 of file netx90_app.h.

| __IM uint32_t aes_Type::in_fifo_overflow |

[14..14] Input FIFO was overflown, set aes_cfg-enable=0 to reset this bit

[8..8] Input FIFO was overflown, set aes_cfg-enable=0 to reset this bit

Definition at line 2828 of file netx90_app.h.

| __IOM uint32_t aes_Type::in_fifo_overflow |

[8..8] Input FIFO was overflown, set aes_cfg-enable=0 to reset this bit

Definition at line 2867 of file netx90_app.h.

| __IM uint32_t aes_Type::in_fifo_underrun |

[13..13] Input FIFO was underrun, set aes_cfg-enable=0 to reset this bit Note: underrun is only a theoretical FIFO status, because the hardware logic of the AES core won't fetch data from the FIFO when it's empty.

[7..7] Input FIFO was underrun, set aes_cfg-enable=0 to reset this bit

Definition at line 2824 of file netx90_app.h.

| __IOM uint32_t aes_Type::in_fifo_underrun |

[7..7] Input FIFO was underrun, set aes_cfg-enable=0 to reset this bit Note: underrun is only a theoretical FIFO status, because the hardware logic of the AES core won't fetch data from the FIFO when it's empty.

[7..7] Input FIFO was underrun, set aes_cfg-enable=0 to reset this bit

Definition at line 2863 of file netx90_app.h.

| __IOM uint32_t aes_Type::in_fifo_wm |

[10..5] Input FIFO watermark level (0..63) used for in_fifo_wm interrupt

[2..2] Fill level of input FIFO is below or equal watermark (see crypt_aes_cfg bits 'in_fifo_wm')

Definition at line 2793 of file netx90_app.h.

| __IM uint32_t aes_Type::in_fifo_wm |

[2..2] Fill level of input FIFO is below or equal watermark (see crypt_aes_cfg bits 'in_fifo_wm')

Definition at line 2892 of file netx90_app.h.

| __IM uint32_t aes_Type::key_exp_ready |

[0..0] Set when key expansion procedure is done

Definition at line 2816 of file netx90_app.h.

| __IOM uint32_t aes_Type::key_exp_ready |

[0..0] Set when key expansion procedure is done

Definition at line 2854 of file netx90_app.h.

| __IOM uint32_t aes_Type::key_exp_start |

[4..4] Start AES key expansion After writing '1', this bit will automatically be reset. Data input can be started when key expansion is ready (see crypt_aes_stat bit 'key_exp_ready').

Definition at line 2790 of file netx90_app.h.

| __IOM uint32_t aes_Type::key_len |

[3..2] AES key length 0: 128 bit 1: 192 bit 2: 256 bit 3: reserved

Definition at line 2789 of file netx90_app.h.

| __IOM uint32_t aes_Type::mode |

[1..1] AES core operation mode 0: Encrypt 1: Decrypt

Definition at line 2788 of file netx90_app.h.

| __IM uint32_t aes_Type::op_ready |

[1..1] Set when AES operation ready, i.e. AES core not busy and input FIFO is empty

Definition at line 2817 of file netx90_app.h.

| __IOM uint32_t aes_Type::op_ready |

[1..1] Set when AES operation ready, i.e. AES core not busy and input FIFO is empty

Definition at line 2855 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_dma_burst_only |

[20..20] Generate DMAC burst signal only (output FIFO). When set to '1' the DMAC logic will only generate burst requests to the DMAC. This is not strictly needed for the DMAC implementation, but could result in better system performance.

Definition at line 2804 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_dma_en |

[19..19] Enable DMAC control signals for the output FIFO.

Definition at line 2803 of file netx90_app.h.

| __IM uint32_t aes_Type::out_fifo_empty |

[22..22] Output FIFO is empty

[10..10] Output FIFO is empty

Definition at line 2831 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_empty |

[10..10] Output FIFO is empty

Definition at line 2871 of file netx90_app.h.

| __IM uint32_t aes_Type::out_fifo_fill |

[21..15] Fill level of output FIFO in bytes (0..64)

Definition at line 2830 of file netx90_app.h.

| __IM uint32_t aes_Type::out_fifo_full |

[24..24] Output FIFO is full

[12..12] Output FIFO is full

Definition at line 2833 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_full |

[12..12] Output FIFO is full

Definition at line 2873 of file netx90_app.h.

| __IM uint32_t aes_Type::out_fifo_not_empty |

[23..23] Output FIFO is not empty

[11..11] Output FIFO is not empty

Definition at line 2832 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_not_empty |

[11..11] Output FIFO is not empty

Definition at line 2872 of file netx90_app.h.

| __IM uint32_t aes_Type::out_fifo_not_full |

[25..25] Output FIFO is not full

[13..13] Output FIFO is not full

Definition at line 2834 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_not_full |

[13..13] Output FIFO is not full

Definition at line 2874 of file netx90_app.h.

| __IM uint32_t aes_Type::out_fifo_overflow |

[27..27] Output FIFO was overflown, set aes_cfg-enable=0 to reset this bit Note: overflow is only a theoretical FIFO status, because the hardware logic of the AES core won't put data into the FIFO when it's full.

[15..15] Output FIFO was overflown, set aes_cfg-enable=0 to reset this bit

Definition at line 2837 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_overflow |

[15..15] Output FIFO was overflown, set aes_cfg-enable=0 to reset this bit Note: overflow is only a theoretical FIFO status, because the hardware logic of the AES core won't put data into the FIFO when it's full.

[15..15] Output FIFO was overflown, set aes_cfg-enable=0 to reset this bit

Definition at line 2877 of file netx90_app.h.

| __IM uint32_t aes_Type::out_fifo_underrun |

[26..26] Output FIFO was underrun, set aes_cfg-enable=0 to reset this bit

[14..14] Output FIFO was underrun, set aes_cfg-enable=0 to reset this bit

Definition at line 2835 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_underrun |

[14..14] Output FIFO was underrun, set aes_cfg-enable=0 to reset this bit

Definition at line 2875 of file netx90_app.h.

| __IOM uint32_t aes_Type::out_fifo_wm |

[16..11] Output FIFO watermark level (0..63) used for out_fifo_wm interrupt

[9..9] Fill level of output FIFO is above watermark (see crypt_aes_cfg bits 'out_fifo_wm')

Definition at line 2795 of file netx90_app.h.

| __IM uint32_t aes_Type::out_fifo_wm |

[9..9] Fill level of output FIFO is above watermark (see crypt_aes_cfg bits 'out_fifo_wm')

Definition at line 2902 of file netx90_app.h.

| __IOM uint32_t aes_Type::val |

[31..0] key bits 31..0

[31..0] key bits 63..32

[31..0] key bits 95..64

[31..0] key bits 127..96

[31..0] key bits 159..128

[31..0] key bits 191..160

[31..0] key bits 223..192

[31..0] key bits 255..224

Definition at line 2998 of file netx90_app.h.

| __OM uint32_t aes_Type::val |

[31..0] data bits

Definition at line 3067 of file netx90_app.h.

| __IM uint32_t aes_Type::val |

[31..0] data bits

Definition at line 3075 of file netx90_app.h.