|

| enum | DRV_SPI_MISO_E {

DRV_SPI_MISO_ACTIVE = 0x0u,

DRV_SPI_MISO_INACTIVE = 0x1u

} |

| | Enumeration of the mosi drive state as slave. More...

|

| |

| enum | DRV_SPI_FSS_E {

DRV_SPI_FSS_NONE = 0x00u,

DRV_SPI_FSS_0 = 0x1u,

DRV_SPI_FSS_1 = 0x2u,

DRV_SPI_FSS_2 = 0x4u,

DRV_SPI_FSS_ALL = 0x7u

} |

| | Enumeration of the frame or slave select (FSS) signal pin mask. More...

|

| |

| enum | DRV_SPI_FREQUENCY_E {

DRV_SPI_FREQUENCY_STOPPED = 0x000u,

DRV_SPI_FREQUENCY_24_4KHz = 0x001u,

DRV_SPI_FREQUENCY_48_8KHz = 0x002u,

DRV_SPI_FREQUENCY_97_6KHz = 0x004u,

DRV_SPI_FREQUENCY_195KHz = 0x008u,

DRV_SPI_FREQUENCY_390KHz = 0x010u,

DRV_SPI_FREQUENCY_781KHz = 0x020u,

DRV_SPI_FREQUENCY_1_56MHz = 0x040u,

DRV_SPI_FREQUENCY_3_125MHz = 0x080u,

DRV_SPI_FREQUENCY_6_25MHz = 0x100u,

DRV_SPI_FREQUENCY_12_5MHz = 0x200u,

DRV_SPI_FREQUENCY_25MHz = 0x400u,

DRV_SPI_FREQUENCY_50MHz = 0x800u,

DRV_SPI_FREQUENCY_99MHz = 0xFFFu,

DRV_SPI_FREQUENCY_MAX = DRV_SPI_FREQUENCY_99MHz,

DRV_SPI_FREQUENCY_MIN = DRV_SPI_FREQUENCY_STOPPED

} |

| | Enumeration of useful spi frequencies. More...

|

| |

| enum | DRV_SPI_BEHAVIOUR_E {

DRV_SPI_BEHAVIOUR_MASTER = 0x0u,

DRV_SPI_BEHAVIOUR_SLAVE = 0x1u

} |

| | Enumeration of the master/slave mode. More...

|

| |

| enum | DRV_SPI_MODE_E {

DRV_SPI_MODE_0 = 0x0u,

DRV_SPI_MODE_1 = 0x1u,

DRV_SPI_MODE_2 = 0x2u,

DRV_SPI_MODE_3 = 0x3u,

DRV_SPI_MODE_MIN = DRV_SPI_MODE_0,

DRV_SPI_MODE_MAX = DRV_SPI_MODE_3

} |

| | Enumeration of the sampling mode. More...

|

| |

| enum | DRV_SPI_SPH_E {

DRV_SPI_SPH_SAMPLE_AT_FIRST_EDGE = 0x0u,

DRV_SPI_SPH_SAMPLE_AT_SECOND_EDGE = 0x1u

} |

| | Enumeration of the serial clock phase. More...

|

| |

| enum | DRV_SPI_DUPLEX_E {

DRV_SPI_DUPLEX_HALF = 0x1u,

DRV_SPI_DUPLEX_FULL = 0x0u

} |

| | Enumeration of the duplex mode. More...

|

| |

| enum | DRV_SPI_PARALLELISM_E {

DRV_SPI_PARALLELISM_1BIT = 0x0u,

DRV_SPI_PARALLELISM_2BIT = 0x1u,

DRV_SPI_PARALLELISM_4BIT = 0x2u,

DRV_SPI_PARALLELISM_MAX = DRV_SPI_PARALLELISM_4BIT,

DRV_SPI_PARALLELISM_MIN = DRV_SPI_PARALLELISM_1BIT

} |

| | Enumeration of the parallelism. More...

|

| |

| enum | DRV_SPI_SPO_E {

DRV_SPI_SPO_CLOCK_INACTIVE_LOW = 0x0u,

DRV_SPI_SPO_CLOCK_ACTIVE_LOW = 0x1u,

DRV_SPI_SPO_CLOCK_INACTIVE_HIGH = 0x1u,

DRV_SPI_SPO_CLOCK_ACTIVE_HIGH = 0x0u

} |

| | Enumeration of the serial clock polarity. More...

|

| |

| enum | DRV_SPI_ENDIANESS_E {

DRV_SPI_ENDIANESS_LITTLE = 0x0u,

DRV_SPI_ENDIANESS_BIG = 0x1u

} |

| | Enumeration of the Endianess used. More...

|

| |

| enum | DRV_SPI_FSS_STATIC_E {

DRV_SPI_FSS_STATIC_HARDWARE = 0x0u,

DRV_SPI_FSS_STATIC_DRIVER = 0x1u,

DRV_SPI_FSS_STATIC_CALLER = 0x11u

} |

| | Enumeration of the frame/chip select modes. More...

|

| |

| enum | DRV_SPI_FIFO_WM_E {

DRV_SPI_FIFO_WM_RESET = 0x0u,

DRV_SPI_FIFO_WM_MIN = 0x1u,

DRV_SPI_FIFO_WM_DEFAULT = 0x9u,

DRV_SPI_FIFO_WM_MAX = 0x10u

} |

| | Enumeration of the water mark level of the fifos. More...

|

| |

| enum | DRV_SPI_FRAME_FORMAT_E {

DRV_SPI_FRAME_FORMAT_MOTOROLA = 0x0u,

DRV_SPI_FRAME_FORMAT_RESERVED0 = 0x1u,

DRV_SPI_FRAME_FORMAT_RESERVED1 = 0x2u,

DRV_SPI_FRAME_FORMAT_RESERVED2 = 0x3u,

DRV_SPI_FRAME_FORMAT_MAX = DRV_SPI_FRAME_FORMAT_MOTOROLA

} |

| | Enumeration of the available frame formats of the spi. More...

|

| |

| enum | DRV_SPI_SLV_SIG_EARLY_E {

DRV_SPI_SLV_SIG_NOT_EARLY = 0x0u,

DRV_SPI_SLV_SIG_EARLY = 0x1u

} |

| | Enumeration of the modes of the early response bit generation. More...

|

| |

| enum | DRV_SPI_FILTER_E {

DRV_SPI_FILTER_INACTIVE = 0x0u,

DRV_SPI_FILTER_ACTIVE = 0x1u

} |

| | Enumeration of the filter state. More...

|

| |

| enum | DRV_SPI_LOOP_BACK_MODE_E {

DRV_SPI_LOOP_BACK_MODE_INACTIVE = 0x0u,

DRV_SPI_LOOP_BACK_MODE_ACTIVE = 0x1u

} |

| | Enumeration of the loop back mode. More...

|

| |

| enum | DRV_SPI_DUMMYPATTERN_E {

DRV_SPI_DUMMYPATTERN_NULL = 0x0u,

DRV_SPI_DUMMYPATTERN_ALTERNATING_0 = 0xAAAAu,

DRV_SPI_DUMMYPATTERN_ALTERNATING_1 = 0x5555u,

DRV_SPI_DUMMYPATTERN_FULL = 0xFFFFu

} |

| | Enumeration of dummy patterns available to send when only one of the full duplex lines are used. More...

|

| |

| enum | DRV_SPI_DATA_SIZE_SELECT_E {

DRV_SPI_DATA_SIZE_SELECT_RESET = 0x0ul,

DRV_SPI_DATA_SIZE_SELECT_4b = 0x03ul,

DRV_SPI_DATA_SIZE_SELECT_MIN = DRV_SPI_DATA_SIZE_SELECT_4b,

DRV_SPI_DATA_SIZE_SELECT_5b = 0x04ul,

DRV_SPI_DATA_SIZE_SELECT_6b = 0x05ul,

DRV_SPI_DATA_SIZE_SELECT_7b = 0x06ul,

DRV_SPI_DATA_SIZE_SELECT_8b = 0x07ul,

DRV_SPI_DATA_SIZE_SELECT_DEFAULT = DRV_SPI_DATA_SIZE_SELECT_8b,

DRV_SPI_DATA_SIZE_SELECT_9b = 0x08ul,

DRV_SPI_DATA_SIZE_SELECT_10b = 0x09ul,

DRV_SPI_DATA_SIZE_SELECT_11b = 0x0aul,

DRV_SPI_DATA_SIZE_SELECT_12b = 0x0bul,

DRV_SPI_DATA_SIZE_SELECT_13b = 0x0cul,

DRV_SPI_DATA_SIZE_SELECT_14b = 0x0dul,

DRV_SPI_DATA_SIZE_SELECT_15b = 0x0eul,

DRV_SPI_DATA_SIZE_SELECT_16b = 0x0ful,

DRV_SPI_DATA_SIZE_SELECT_MAX = DRV_SPI_DATA_SIZE_SELECT_16b

} |

| | Enumeration of the data size of a word transmitted. Has no impact on SQI devices. More...

|

| |

| enum | DRV_SPI_STATE_E {

DRV_SPI_STATE_RX_FIFO_UNDERRUN = 0x1u << 31u,

DRV_SPI_STATE_RX_FIFO_OVERFLOW = 0x1u << 30u,

DRV_SPI_STATE_RX_FIFO_LVL_16b = 0x10u << 24u,

DRV_SPI_STATE_RX_FIFO_LVL_08b = 0x8u << 24u,

DRV_SPI_STATE_RX_FIFO_LVL_04b = 0x4u << 24u,

DRV_SPI_STATE_RX_FIFO_LVL_02b = 0x2u << 24u,

DRV_SPI_STATE_RX_FIFO_LVL_01b = 0x1u << 24u,

DRV_SPI_STATE_TX_FIFO_UNDERRUN = 0x1u << 23u,

DRV_SPI_STATE_TX_FIFO_OVERFLOW = 0x1u << 22u,

DRV_SPI_STATE_TX_FIFO_LVL_16b = 0x10u << 16u,

DRV_SPI_STATE_TX_FIFO_LVL_08b = 0x8u << 16u,

DRV_SPI_STATE_TX_FIFO_LVL_04b = 0x4u << 16u,

DRV_SPI_STATE_TX_FIFO_LVL_02b = 0x2u << 16u,

DRV_SPI_STATE_TX_FIFO_LVL_01b = 0x1u << 16u,

DRV_SPI_STATE_BUSY = 0x1u << 4u,

DRV_SPI_STATE_RX_FIFO_FULL = 0x1u << 3u,

DRV_SPI_STATE_RX_FIFO_NOT_EMPTY = 0x1u << 2u,

DRV_SPI_STATE_TX_FIFO_NOT_FULL = 0x1u << 1u,

DRV_SPI_STATE_TX_FIFO_EMPTY = 0x1u << 0

} |

| | Enumeration of the spi state informations. More...

|

| |

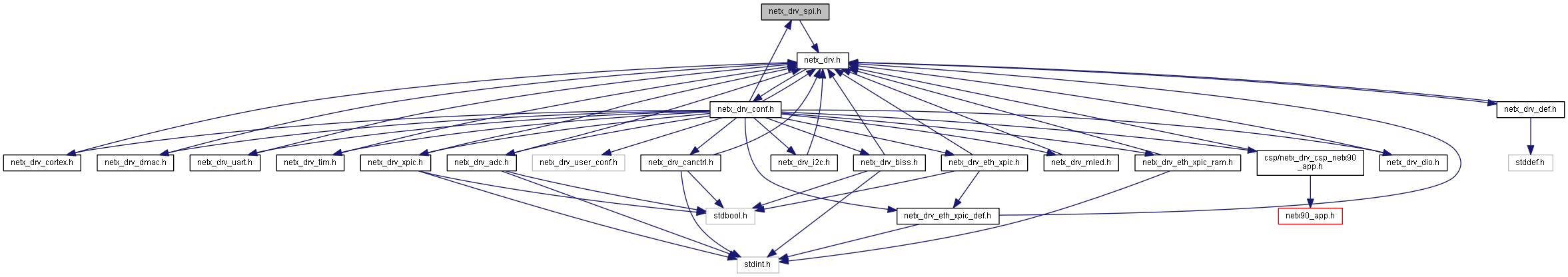

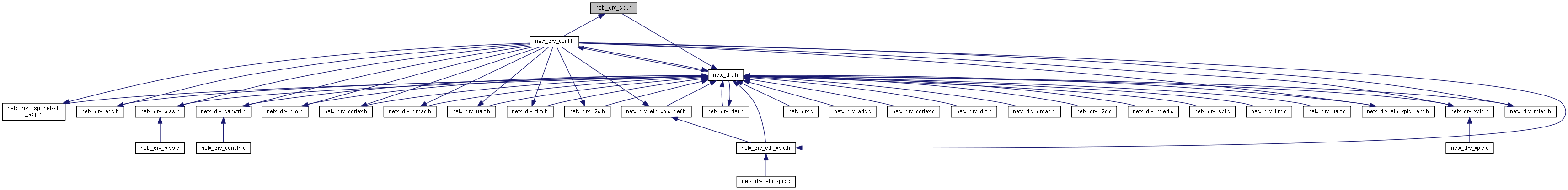

Header file of GPIO DRV module.

- Revision

- 6251

- Date

- 2019-10-07 09:27:10 +0200 (Mo, 07 Okt 2019)

- Copyright

- Copyright (c) Hilscher Gesellschaft fuer Systemautomation mbH. All Rights Reserved.

- Note

- Exclusion of Liability for this demo software: The following software is intended for and must only be used for reference and in an evaluation laboratory environment. It is provided without charge and is subject to alterations. There is no warranty for the software, to the extent permitted by applicable law. Except when otherwise stated in writing the copyright holders and/or other parties provide the software "as is" without warranty of any kind, either expressed or implied. Please refer to the Agreement in README_DISCLAIMER.txt, provided together with this file! By installing or otherwise using the software, you accept the terms of this Agreement. If you do not agree to the terms of this Agreement, then do not install or use the Software!

Definition in file netx_drv_spi.h.