|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

|

Hilscher netX microcontroller driver

V0.0.5.0

Documentation of the netX driver package

|

This is the driver library, designated for the netX microcontroller application side. This page will provide an overview of the driver and explain how it is structured and how it is used. The target IDE of this introduction and the driver itself is netX Studio.

The CMSIS component is also used and explained here. In future versions both components will be merged together.

The target of the driver layer is to provide a simple API for the applications to interact with the devices available. We have two kinds of drivers. The first one are the ones we have developed after the CMSIS recommendations. The other ones are developed for verification purposes and provide a hardware near abstaction layer. To support the family of chips a so called chip support layer was introduced, where the drivers functionality is mapped to requirement definitons and of course the hardware registers.

This meta layer shall met the following requirements:

The following devices are supported with full drivers:

The following devices are supported by legacy drivers:

To illustrate the structure of the driver an example device driver "DEV" is discussed. The naming convention and other ones will be discussed in the next chapter called "Conventions".

Most of our peripherals are communication devices or deliver an data stream of some kind. Those streams are in most concepts transmitting and receiving data in single-, half- or full-duplex. To increase the maintainability the data and the control flows are split up as good as possible. To transport the data, the dma is used or the flush routine for transmitting the data. All other functions have the job to configure, initiate and control the flow of data.

In the layer model below one is able to see its over all structure. At the top there is an application and in the bottom, the hardware peripherals are shown.

| Application | ||||||

|---|---|---|---|---|---|---|

| CMSIS, OS abstaction and helper functions | DRV_DEV_GetState/ DRV_DEV_Init | DRV_DEV_Abort | DRV_DEV_Tx | DRV_DEV_Rx | DRV_DEV_TxRx | |

| CallByControlFlow | ||||||

| DMA | IRQ | Poll | IRQ | DMA | ||

| ISR | DMA ISR | |||||

| Flush | ||||||

| Hardware Device/NVIC/DMAC | ||||||

Between the application and the hardware are on the upper layer the API calls. Some are directly interacting with the hardware like the initialization and some are not. The get state for example derives hardware states and software states in one call. The init function for example talks also with the NVIC peripheral and the dmac to initialize the drivers context by its given configuration. The abort function is split between the dma and irq mode but for polling it is not necessary, because in polling it is not possible to abort the polling context. To centralize the control flow and to switch between data direction and operation method there is a special layer. That configures the data flow parameters and then calls the associated operation method. This is done, because in most cases, the operation mode is independent of the data flow configured.

The driver is configured by a configuration file. This file is called netx_drv_user_conf.h, which is derived from its template called netx_drv_user_conf_template.h.

The configuration file may be used to include components of the driver into the build process or not, without managing the inclusion inside waf and the sources. This may be performed my commenting out or in the enabled macros.

It is also used for the os specific parts of the driver, where it is possible to exchange the api locking with the os free mutexes against os specific ones.

Because the DMA is used by some other drivers it has to be included if those are used. The same will be necessary for the SQI-Flash driver with the SQI driver.

The os abstraction layer currently exists solely by the locking mechanism of the API. If a context is already in use, the locking mechanism shall prevent two callers from using the same context. Two callers for example might be on the netX90 two tasks of an operating system or the normal execution context (user mode) and the interrupt context (privileged mode).

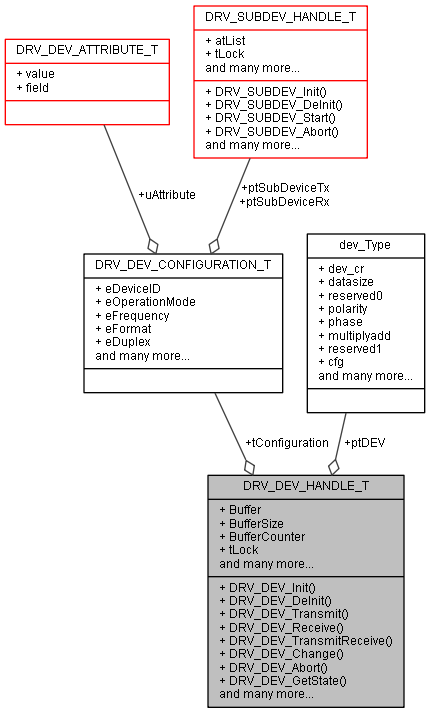

In the diagram below, one is able to take a look on the general structure of drivers. The first attribute of all function calls shall contain a pointer to the structure containing the execution context. The only exception of this are the DIO driver, that has a global context objet and the legacy hardware abstraction layer drivers.

The handle structure associated with the device consists out of the configuration, other attributes and a set of functions. The attributes shall not be altered, except the configuration, which shall be provided before (re)initializing the driver. So it is possible to change configuration parameters afterwards, but they have to be followed by an initialization. This has a lot of side effects and should only be performed if really necessary. The change of operation mode by reinitilization is particularly not recommended at the moment, because of its huge test vector.

In case that a subdevice is used, such as the dma controller, one has to provide a context handle.

The driver has the legacy HALs that are not part of this structure, also the dio driver is a bit special. The DIO has a global handle, that is not visible to the user. This design choice was made, because the devices have no interleaved configuration and no higher context. Each channel (pin) has a well defined state so that it is not necessary to provide context sensitive informations between interactions.

The normal API however has some core functions. As already used in the class diagram above, we define a device called DEV by functionalities as init, deinit, transmit, receive, change, abort and at last get state. All methods return the state of the drivers api. In c peudo code, such a device interaction is shown. The example is some kind of spi device, where the chip or frame select line is set before and reset after a transmission.

The data and the control instructions are split up into several contexts. While the data and the control instructions originate from the same source, they should be split up as early as possible and executed by different (meta) contexts. Those conexts and the execution Sequence of the

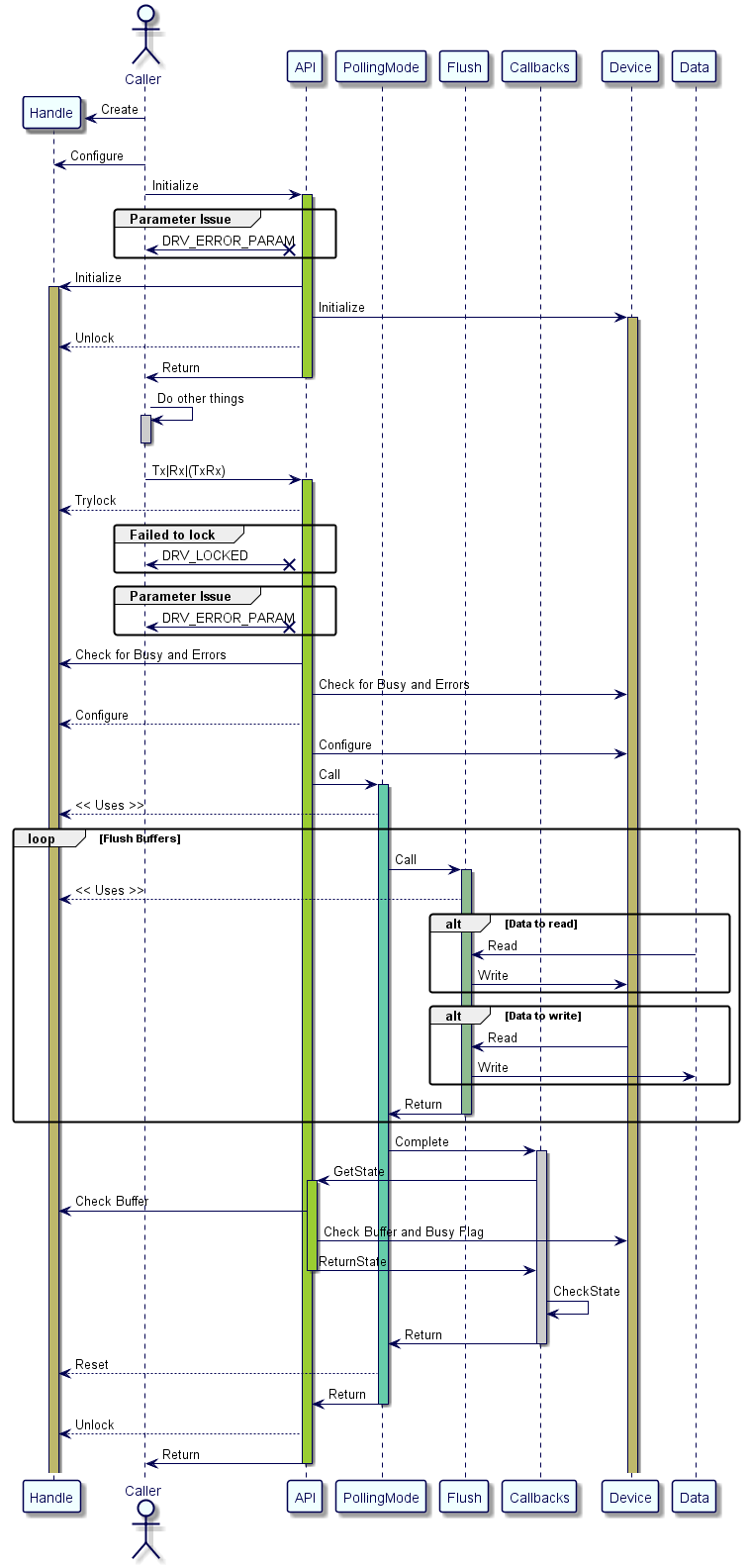

The polling mode of an driver is intended to give the user a mode where the device is acessed in high priority by the core to exchange data. This means, that the caller context is blocked and its primary task is to flush the buffers. In the sequence diagram below one can see how this behaviour is achieved.

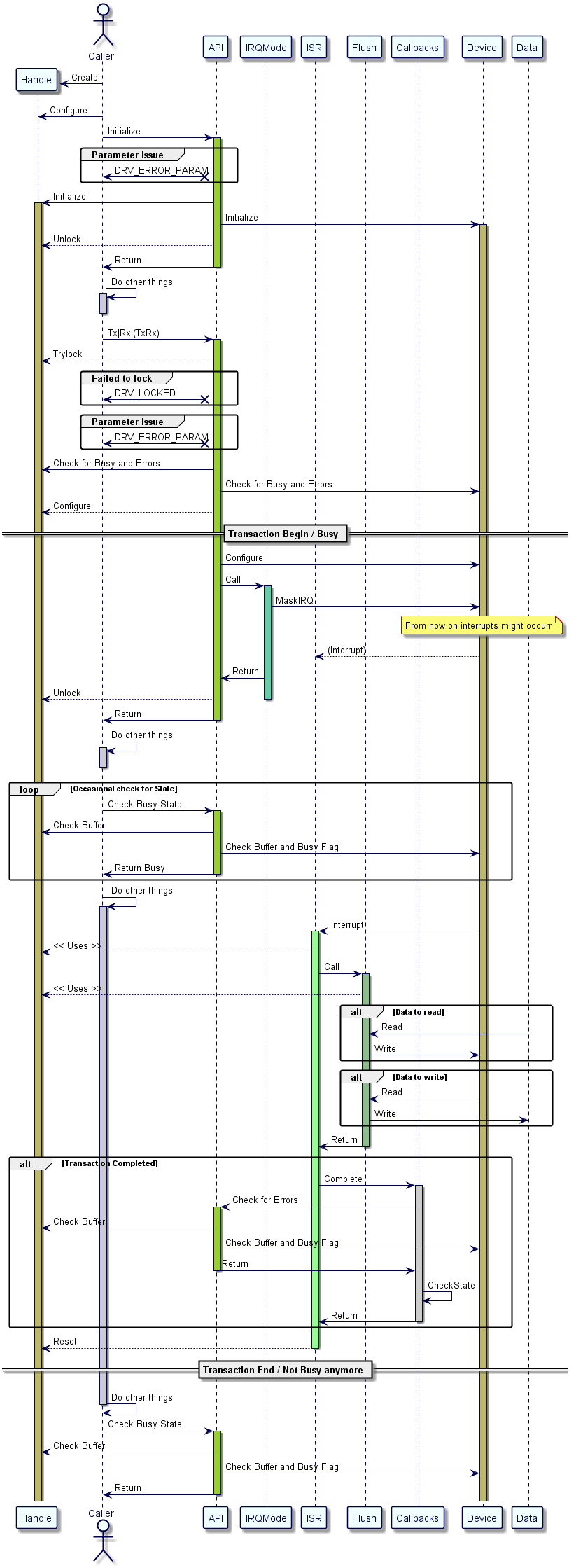

This shall be an explatory text for the IRQ Mode.

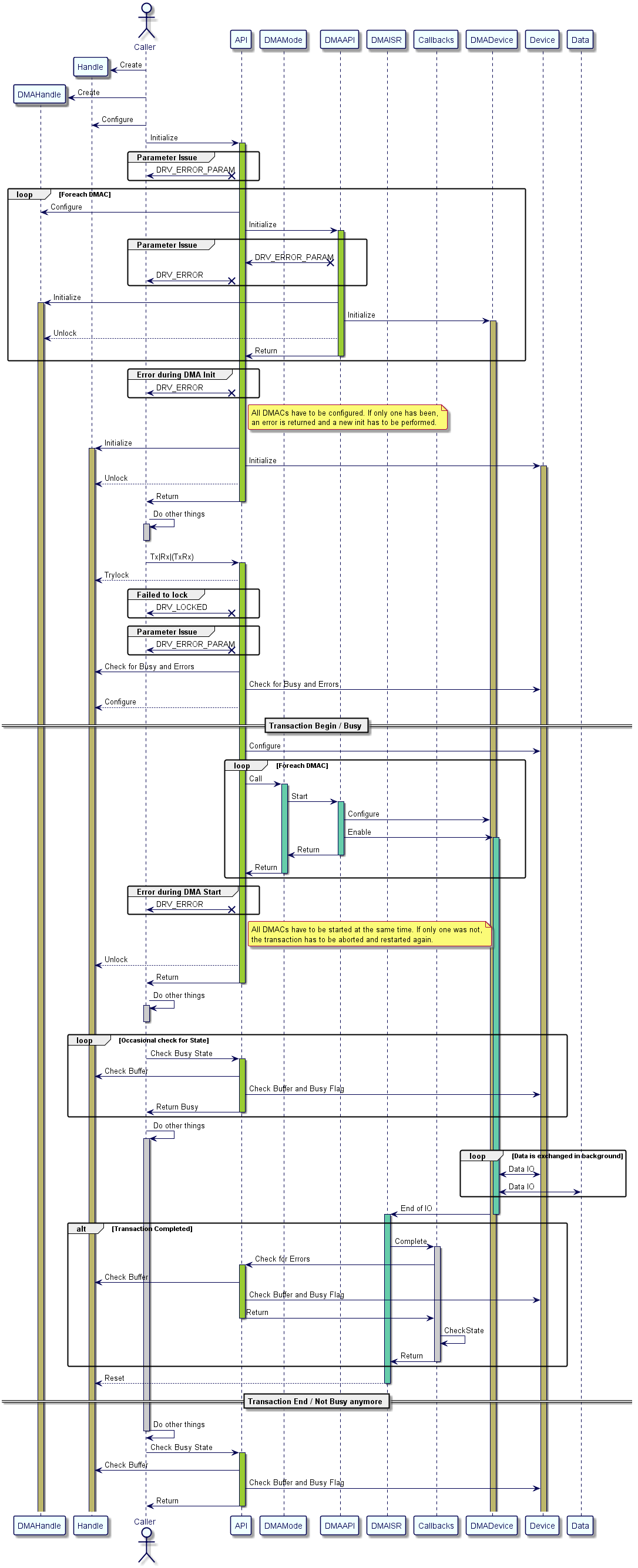

This shall be an explatory text for the DMA Mode.

The following code snipped is an example code on how to make use of the returned state. Not every DRV_STATE_E differing from DRV_OK is an error. A good example might be the DRV_LOCKED state, which might occur because an interrupt interrupted the allocation of the locking mutex. If this has happened one has to try again locking it. However, the API might also be locked and another task is using it. So it is feasible to log the time or count how often this happens and decide at wich point this might be an error.

We would like to give an introduction in the conventions used in this library.

As a naming convention we will use a namespacing scheme. Every driver call or data type will be prefixed with "DRV_" and the files with "netx_drv_". After those prefixes the next part will be the drivers module name like "DRV_SPI", which is in this case the SPI module.

All files shall be prefixed by "netx_drv". Thus for example the spi driver would be named netx_drv_spi. The suffix shall suffice the language requirements. So C source files are suffixed with ".c" and the headers with ".h". In the case of C++ the sources are suffixed with ".cpp" and the headers with ".hpp". Assembler files with ".S" or ".s". The CMSIS SVD file has the suffix ".svd" and documentations end with ".txt". The waf script is without any suffix and named unique by folder as wscript.

After the drivers prefix DRV_ the device is specified with a short naming in capital letters DRV_DEV

The enumerations will all be prefixed with DRV_ and then followed by the device for which they are defined. Then the name of the enumeration is given in capital letters DRV_DEV_ENUM_E

DRV_DEV_SOMETHING

struct DRV_DEV_STRUCT_Ttag

DRV_DEV_STRUCT_T

__NVIC and so on.

DRV_DEV_Init

enum eVariableValue

There shall be documentation everywhere

At the beginning. The doxygen grouping. Disclaimer

Before the types definition. Each structure or enum element

Before the function in the header brief with member of and in the source detailled with member of, params return and visibility.

The drivers are designed in the way that a caller is able to allocate the context handle on its stack. The drivers do not allocate memory on themselfs. Also the drivers API is protected with an os free mutex implementation for locking. This of course might be exchanged with operating system functions. So in drivers default, it is always possible to analyze the used stack memory with call graphs.

The driver has a file called user_drv_conf_template.h which shall be copied/renamed to user_drv_conf.h and modified. The driver has to be build without any extra parameters necessary. The CMSIS compliant device description header files and starting code has to be used. In the templates and Examples provided from hilscher are waf scripts. Those scripts contain the script parts necessary for compiling the driver.

The driver component depends on the CMSIS component and both shall be used together.

In the waf scripts we recommend the following compiler options:

The example linker scripts are available in the CMSIS folder.

| Version | Date | Who | Description |

|---|---|---|---|

| V0.0.5.0 | 2019-12-17 | AGR | Header changes |

| V0.0.4.10 | 2019-12-16 | AGR | XPIC Hotfix |

| V0.0.4.9 | 2019-12-05 | AGR | SPI and UART Hotfix |

| V0.0.4.8 | 2019-10-07 | AGR | CMSIS Temperature Support |

| V0.0.4.7 | 2019-05-14 | AGR | CMSIS Template ld |

| V0.0.4.6 | 2019-05-02 | AGR | TIM Hotfix |

| V0.0.4.5 | 2019-04-25 | AGR | Info Page Fix |

| V0.0.4.4 | 2019-04-17 | AGR | Production Tested Chips |

| V0.0.4.3 | 2018-12-18 | AGR | End of year |

| V0.0.4.2 | 2018-11-22 | AGR | Trading Show Beta |

| V0.0.4.1 | 2018-11-15 | AGR | First Hotfix Round |

| V0.0.4.0 | 2018-11-13 | AGR | Final Silicon Pre-Beta |

| V0.0.3.0 | 2018-07-20 | AGR | DMA Pre-Beta |

| V0.0.2.0 | 2018-03-01 | AGR | CAN Pre-Beta |

| V0.0.1.0 | 2018-01-26 | AGR | Pre-Beta |

| V0.0.0.3564 | 2018-01-16 | AGR | Alpha |

| V0.0.0.3452 | 2017-11-06 | AGR | Pre-Alpha |

Changed the wscript and tagged basically the V0.0.4.10 again due to the changes in driver and CMSIS regarding the headers linker files and everything that was part of V0.0.4.9 and V0.0.4.10

This release shall have the support for the final silicon of the netX90 chip. Also the MLED module, the SQI devices, the ADC device for the final and the ethernet_mac_xpic device drivers are included.

This release introduces the chip support layer and it contains changes to some drivers and also new ones. It also renames all driver files regarding the namespace convention.

The canctrl driver was added to support can functionality. NOTE: The driver is just a temporary implementation and might be replaced in the future.

First release contains everything until today. (V0.0.0.3452, V0.0.0.3452) Since last version

Documentation in HTML-format can be generated by using doxygen. A respective Doxyfile is part of this example. You can run doxygen from command line or from inside netX Studio CDT. The output will be created in folder Doc.

Just click on @ symbol at menu bar and choose Doxyfile. At the first time using this, netX Studio CDT will ask for installing Doxygen and Graphviz, which have to be installed.

Just execute doxygen from command line in the root directory of this example. It is required to have doxygen.exe in the PATH. If the "graphviz" package is installed, the documentation contains visual dependency diagrams. Due to a bug in dogygen, it is necessary to specify the path to dot.exe (Graphviz) in the "Doxyfile" -> DOT_PATH parameter

Exclusion of Liability for this demo software: The following software is intended for and must only be used for reference and in an evaluation laboratory environment. It is provided without charge and is subject to alterations. There is no warranty for the software, to the extent permitted by applicable law. Except when otherwise stated in writing the copyright holders and/or other parties provide the software "as is" without warranty of any kind, either expressed or implied.